# 2025 International Solid-State Circuits Conference

# (ISSCC) Review

연세대학교 디스플레이융합공학과 최우준 교수

**Topic: Analog**

## **Session 3 : Amplifiers and Analog Front-Ends**

Session 3 Amplifiers and Analog Front-Ends 에서는 Class-D amplifier, Instrumentation amplifier, Multimode amplifier 등 총 4편의 논문이 발표되었다. 작년 Session 21 Audio amplifier과 비교하여 다양한 Front-end 구조 및 폭넓은 Application에 적용된 Amplifier 관련 논문을 확인할 수 있었다. 이 중 Passive switched-capacitor-based multi-mode amplifier와 Self-trimmed CMOS operational amplifier에 대한 2개의 논문을 살펴보고자 한다.

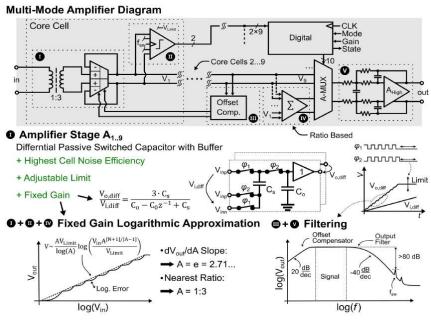

#3-3 본 논문은 Leibniz University Hannover에서 발표한 논문으로, 본 논문은 지열 에너지 발전에 활용될 수 있도록 약 200℃ 환경에서, 100dB 이상의 넓은 DR을 갖는 Multi-mode amplifier를 제 안한다. 해당 Amplifier는 Logarithm, Programmable gain, Automatic gain control 등 3가지 모드를 지원하여 다양한 사용 환경에 적용될 수 있다. 특히 범용적인 DC-DC converter와 Series-parallel amplifier에 활용되었던 Switched capacitor 구조의 Cell을 활용하여 PVT 변화에 강한 Gain과 높은 Noise efficiency를 동시에 구현하였다. 해당 Cell을 Cascade stage를 구성함과 동시에 Limiter를 통하여 Automatic gain control 및 Piecewise logarithmic amplification 기능을 구현하였다. 그 결과로서, -25~200℃의 온도 범위에서 0.75%의 Logarithmic conformity error를 달성하였다. 별도의 Trimming이 추가적으로 필요하지 않으며, 극한의 온도 환경에서도 안정된 성능을 제공할 수 있다. 이는 지열과 같은 신재생 에너지원 활용에 적합한 솔루션이 될 것으로 기대한다.

[그림 1] #3-3 논문에서 제안하는 Passive switched-capacitor 기반 Multi-mode amplifier

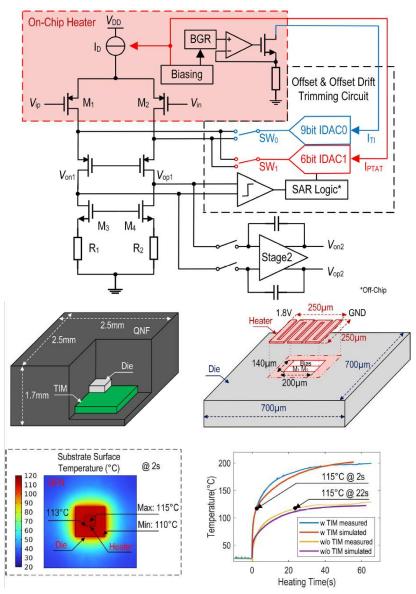

#3-4 본 논문은 Tsinghua university와 TU Delft에서 발표한 논문으로, 본 논문은 저비용의 온칩 히터 기반 2-point self-trimming 기술을 제안한다. 2개의 다른 온도 계수를 갖는 Current DAC을 기반으로 입력 트랜지스터에 대한 Bias를 조절하며, SAR loop를 통해 2개의 온도 지점에서 오프셋 전압을 보정한다. 기존의 Trimming 방식과 비교하여, 제안하는 기술은 소요 시간을 분 단위에서 초 단위로 단축할 수 있으며, 패키징 과정 이후에도 해당 기술을 간단하면서 빠르게 적용할 수 있다. 이를 통하여 양산 과정에서 뿐만 아니라 필요한 경우 사용 환경에서도 지속적인 보정이 가능하다. 제안하는 기술을 적용한 Opamp는 0.18μm CMOS 공정에서 제작되었으며, 실온에서 ±5.8μV (3σ)의 오프셋 전압을 달성하며, -40℃에서 125℃까지 ±88nV/℃(3σ)의 최고 수준의 오프셋 변화를 유지한다. 이는 기존 논문과 비교하여 각 7.7배 및 3.7배 향상된 성능에 해당한다. 히터를 동작시키기 위하여 1.6mW의 큰 전력 소모가 발생할 수 있지만 보정 과정에서만 사용되므로 범용적인 Opamp 사용에 적합할 것으로 예상한다.

[그림 2] #3-4 논문에서 제안하는 온칩 히터를 내장한 Miller-compensated opamp

## Session 4: Analog Techniques

Session 4 Analog Techniques 에서는 ADC front-end, Frequency generation module, Crystal oscillator, Class-D amplifier, RC oscillator, Voltage reference 등 총 6편의 논문이 발표되었다. 작년 과 유사하게 Oscillator 혹은 Amplifier에 치중되지 않고 광범위한 Analog circuit technique을 확인 할 수 있었다. 이 중 Reference-replication 기반 RC oscillator와 3nm FinFET 공정의 Voltage reference에 대한 2개의 논문을 살펴보고자 한다.

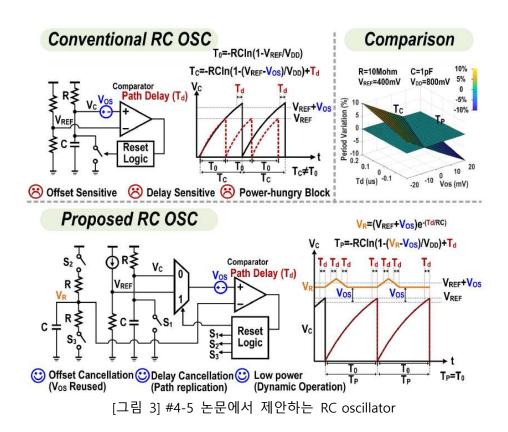

#4-5 본 논문은 University of Electronic Science and Technology of China에서 발표한 논문으로, 본 논문은 Reference-Replication 기술을 적용한 RC relaxation oscillator를 제안한다. 온도에 민감한 Path delay와 Comparator offset 정보를 Reference-replication path에 저장하여 두 요소를 동시에 보정할 수 있도록 설계하였다. 또한, Dynamic loop control를 적용하여 전력 소모를 효과적으로 절 감할 수 있었다. 제안하는 RC oscillator는 65nm CMOS 공정에서 10MHz의 출력 주파수를 구현하였으며, 4.06μW의 전력을 소비하여 0.4μW/MHz의 높은 전력 효율을 달성하였다. 또한, -40℃에서 125℃의 온도 범위에서 9.83ppm/℃의 우수한 온도 계수를 달성하였으며, 전체 면적은 0.0085mm²으로 기존 논문 대비 높은 집적도를 제공한다.

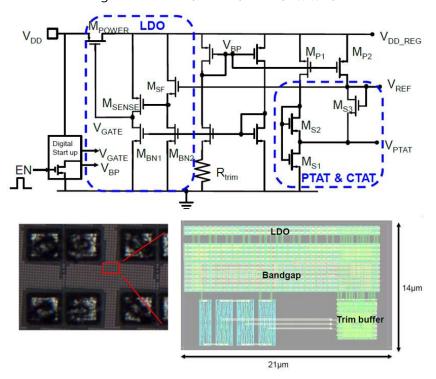

#4-6 본 논문은 TSMC에서 발표한 논문으로, 본 논문은 3nm FinFET 공정에서 CMOS 기반 Voltage reference를 제안한다. 해당 Reference에서는 모든 트랜지스터를 표준 Threshold voltage 타입으로 사용하며, 또한 모든 소자는 단위 FinFET 셀을 직렬 또는 병렬로 연결하여 구현된다. 이를 통해 소자 간 Dimension 차이에 따른 Side effect를 근본적으로 제거할 수 있다. Reference

voltage를 생성하기 위하여 PTAT과 CTAT voltage는 전통적인 Weak inversion 영역의 2-Transistor 회로를 기반으로 구현된다. 1V 미만의 낮은 전원 전압에서 동작 가능하고, 5T LDO를 내장하여 270MHz 대역폭까지 높은 PSR 성능을 확보하였다. 제안하는 Voltage reference는 0.8V 전원에서 15μA 전류를 소모한다. -40°C에서 125°C까지 출력 전압의 평균값은 582mV이며, Trimming 없이 48개의 샘플에 대하여 온도 부정확도는 2.1% (3σ 환산 시 3.4%)이다. 추가적인 Trimming 후에는 부정확도를 1% 이하로 줄일 수 있다. Line sensitivity는 0.75V~0.85V 범위에서 0.04%/V, PSR은 10kHz~100MHz 범위에서 -50dB 이하를 달성했으며, 100MHz~1GHz에서도 -40dB 이하의 성능을 유지함으로써 우수한 Power supply noise rejection 결과를 보여주었다. 또한 다른 논문과 비교할 때 초미세공정에서 가장 작은 294um²의 면적으로 구현되었을 뿐만 아니라, 높은 PVT robustness를 가질 수 있는 고성능 Voltage reference 기술을 확인할 수 있었다.

[그림 4] #4-6 논문에서 제안하는 3nm-FinFET voltage reference

## 저자정보

## 최우준 교수

● 소 속 : 연세대학교 디스플레이융합공학과

연구분야: Display IC Systems, Sensor Interfaces,

Biomedical Circuits and Systems, Analog/Mixed-Signal ICs

• 이 메일: wjchoi11@yonsei.ac.kr

• 홈페이지: https://sites.google.com/view/ysicsl

# 2025 International Solid-State Circuits Conference (ISSCC) Review

한양대학교 ERICA 전자공학부 김종석 교수

**Topic: Sensor**

## Session 6: Imagers and Displays

ISSCC 2025의 Session 6는 Imagers and Displays 라는 주제로 총 10편의 논문이 발표되었다. 이 세션에서는 LiDAR 센서, CMOS 이미지 센서, OLED 디스플레이 드라이버, 터치스크린 컨트롤러에 이르는 다양한 센서 회로 및 디스플레이 회로 연구들이 다수 발표되었다.

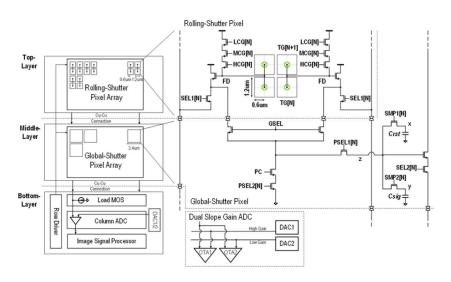

#6-1 삼성전자, 모바일 애플리케이션을 위한 전환 가능한 3층 적층 hybrid shutter (HS) CMOS image sensor (CIS)를 제안하였다. 이 센서는 1.2μm-pitch 50Mpixel rolling shutter (RS)와 2.4μm-pitch 12.5Mpixel global shutter (GS) 모드 간 전환이 가능하다. RS 모드는 30FPS로, GS 모드는 95FPS로 작동한다. Shutter회로는 65nm CIS 공정, logic은 28nm CMOS 공정을 통해 제작되었으며, 3층 적층 구조로 상층은 RS용, 중간층은 GS용, 하층은 logic 회로용으로 설계되었다. 기존 RS CIS 의 성능과 기능을 유지하기 위해 상층에는 conventional 4-transistor pixel 구조를 적용했으며, GS 모드에서의 random noise (RN) 성능 향상을 위해 중간층에 고용량 DRAM capacitor 기술을 적용하였다. 이를 통해 low conversion gain (LCG)에서 52ke-의 full well capacity (FWC), high conversion gain (HCG)에서 2.4e-의 낮은 RN을 달성했다. 또한 high dynamic range (HDR)를 위해 dual slope qain (DSG) 모드를 적용하여 HDR 성능을 6dB 향상시켰다.

[그림] #6.1 논문에서 제안하는 3층 적층 HS 구조.

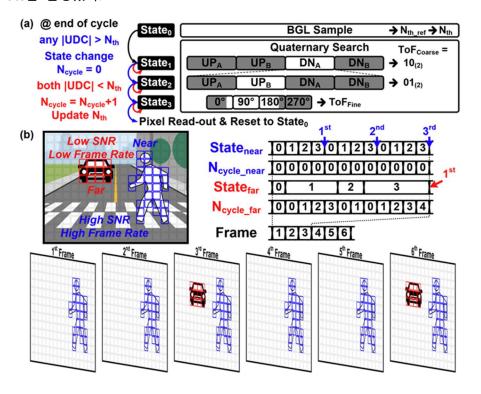

#6-2 UNIST, 외부 구성요소 의존 없이 pixel 자체적으로 threshold ( $N_{th}$ )을 제어하는 background light (BGL) 적응형 Nth 기반 asynchronous  $160 \times 90$  pixel array 플래시 LiDAR 센서를 제안하였다. 기존 LiDAR 센서가 최악의 SNR 조건을 갖는 pixel에 의해 프레임 속도가 제한되는 것과 달리, 제 안하는 LiDAR 센서는 각 pixel이 BGL 강도로부터  $N_{th}$ 를 설정해 time-of-flight (ToF) 값을 검증하고 integration time을 동적 조절한다. Bitwise arithmetic unit으로 pixel 내  $N_{th}$  계산이 가능하며, 검증된 pixel만 순차적으로 읽어낸다. 90nm BSI 공정으로 제작되었으며, 센서는 1.5-to-22.5m 범위에서 6cm precision, 8cm accuracy를 달성했고, 30klux 조명에서도 21m 거리에서 95% 이상 true detection rate를 달성했다.

[그림] #6.2 논문에서 제시된 asynchronous pixel의 개념적 작동 원리.

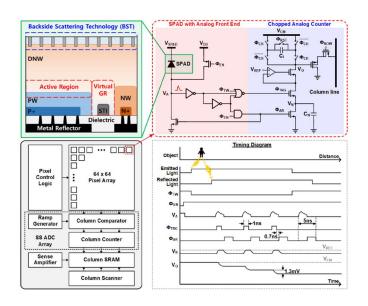

#6-3 연세대학교, 76m 거리와 120klx background light (BGL)에서 작동하는 single-photon avalanche diode (SPAD) 기반 flash LiDAR 센서를 제안했다. 핵심 기술은 BGL을 억제하면서 노출시간을 유지하는 multiple-chopping analog counter 이다. 기존 analog counter 의 선형성 제한 및 BGL 에 의한 saturation 문제를 해결하기 위해 chopped charge-injection 방식을 제안했다. 이 방식은 one discharge path를 사용하여 균일한 counting step을 제공하고 gain mismatch 문제를제거했다. 제안하는 회로는 110nm BSI CIS 공정으로 제작되었으며, multiple-chopping 기술을 통해 counter saturation issue를 해결하여 120klx 의 BGL 의 조건하에 최대 76m 거리에서 6.4cm 의 depth precision, 33%의 fill factor를 달성했다.

[그림] #6.3 논문에서 제안하는 SPAD-based iToF sensor의 구조 및 동작.

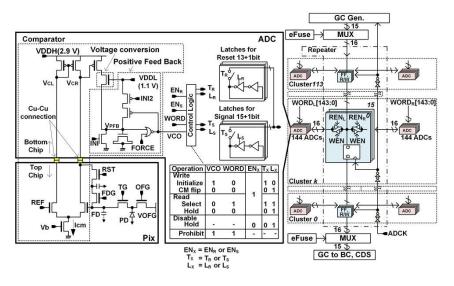

#6-5 SONY, Pixel-parallel ADC를 활용한 25.2Mpixels, 120 FPS full-frame global shutter (GS) CMOS 이미지 센서를 제안했다. Rolling shutter (RS) 센서의 움직이는 물체 왜곡, flicker effect, flash band 문제를 해결하기 위해 global shutter (GS) 기술을 적용했다. Pixel-parallel ADC의 parallelism을 활용하여 ADC comparator 소비전류를 25nA로 감소시켰고, ADC의 comparator에 NMOS capacitor를 추가하여 random noise를 줄였다. Back-illuminated pixel chip은 90nm, logic chip은 40nm 공정을 이용해 제작하였으며, back-illuminated pixel chip과 logic chip을 3µm pitch의 Cu-Cu hybrid bonding으로 연결시켰다. 사용된 ADC는 5.94µm pitch의 single-slope pixel-parallel ADC로 0dB gain에서 2.66 e-rms의 random noise와 14bit resolution을 달성하였다. 따라서 본 논문에서 제안한 CMOS 이미지 센서는 14bit resolution으로 25.2Mpixels을 120FPS에서 판독할 수 있으며, 75.5dB의 dynamic range와 1545mW의 소비전력, 0.083e-rms·pJ/step의 FoM을 달성했다.

[그림] #6.5 논문에서 제안하는 이미지 센서 readout 회로의 구조.

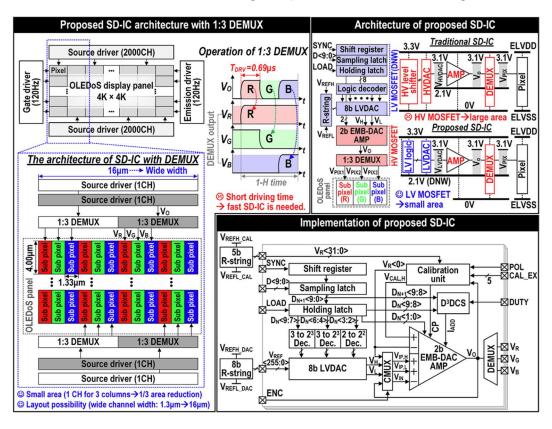

#6-7 한양대학교, AR/VR 기기용 OLED-on-Silicon (OLEDoS) display를 위한 10bit source driver IC 로, 저면적, 고균일, 고속구동의 특성을 갖는다. All-channel automatic offset calibration (ACAOC)를 통해 모든 AMP의 offset 전압을 동시에 보상하여 채널간 균일도를 향상시켰으며, data-difference-dependent dynamic current source (D³DCS)을 통해 대기전류 증가 없이 slew-rate를 향상시켜 구동속도를 향상시켰다. 또한 1:3 demultiplexer (DEMUX) 구조 및 low-voltage (LV) DAC기술을 적용하여 회로 면적을 감소시켰다. 제안하는 회로는 65nm CMOS 공정으로 제작되었으며, channel당 2,273µm²의 면적, 1.9mV의 deviation of voltage outputs (DVO), 0.69µs의 settling time을 달성했다.

[그림] #6.7 논문에서 제안하는 SD-IC의 구조.

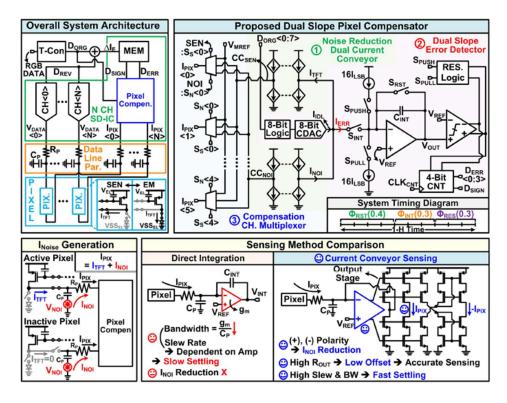

#6-8 고려대학교, AMOLED 디스플레이용 external compensation circuit으로, 패널 pixel 회로의 error를 실시간으로 보상하는 특징을 갖는다. Noise-reduction dual current conveyor (NDCC)를 사용하여 display panel noise로부터 간섭을 받지 않으면서, OLED pixel에 사용된 low-temperature polycrystalline silicon (LTPS) thin-film transistor (TFT)의 non-uniformity를 감지한다. 특히 mismatch 에 민감한 integrator를 필요로 하지 않는 dual slope error detector (DSED)를 통해 pixel error를 감지한다. 또한 compensation channel multiplexer (CCM)를 통해 하나의 compensator가 여러 source driver channel을 지원할 수 있게 하여 회로 면적과 전력소비를 크게 줄였다. 250nm 2.5V/5V 공정으로 제작되었으며, channel당 4442.8μm²의 면적과 13.3μW의 전력소비를 달성했으며, 300kHz에서 최대 630nApp의 panel noise tolerance를 달성했다.

[그림] #6.8 논문에서 제안하는 pixel compensator 의 구조 및 동작.

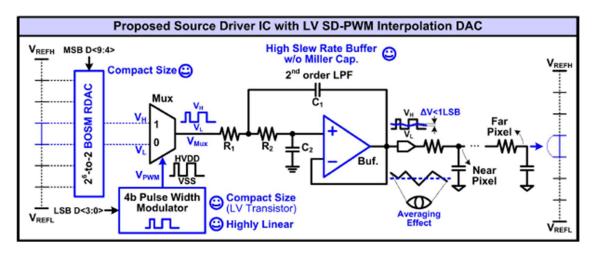

#6-9 고려대학교, 디스플레이용 10bit source driver IC로, delta-sigma pulse width modulation (SD-PWM)을 활용한 low-voltage digital interpolation을 통해 면적을 크게 감소시킨 특징을 갖는다. 4bit low-voltage pulse width modulator와 second-order RC low-pass filter 구성의 SD-PWM interpolation DAC와 MSB switching binary-tree overlap switch merging (BOSM) 기술로 6bit resistor-string DAC의 transistor 수를 80.7% 감소시켰다. 65nm CMOS 공정으로 제작되었으며, 최대 DNL 0.42LSB, 최대 INL 1.44LSB, static current 1.5µA, channel 당 1884µm²의 면적을 달성했다.

[그림] #6.9 논문에서 제안하는 10bit SD-IC의 구조 및 동작원리.

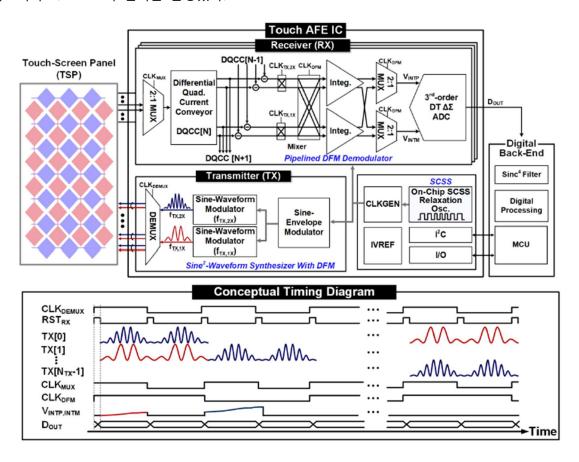

#6-10 성균관대학교, 자동차용 터치스크린 센서를 위한 electromagnetic interference (EMI) 감소 기술을 적용한 touch analog front-end (AFE) integrated circuit을 제안했다. 자동차용 터치스크린 센서는 EMI를 방출하여 차량 내 다른 전자 부품에 영향을 줄 수 있는데, 이 문제를 해결하기 위해 sine² waveform shaping 기술, sine-chirp spread spectrum (SCSS) clocking, 그리고 pipelined dual-frequency modulation (DFM) 방식을 도입했다. 80nm CMOS 공정으로 제작되었으며, CISPR 25 Class 5 규격을 준수하면서도 높은 SNR(최대 49.6dB)과 frame rate(200Hz)를 달성했으며, 10.5mW의 전력소비와 2.21mm²의 면적을 달성했다.

[그림] #6.10 논문에서 제안하는 터치 AFE IC의 구조와 timing diagram.

#### Session 27: Sensor Interfaces

ISSCC 2025의 Session 27은 sensor interfaces 라는 주제로 총 5편의 논문이 발표되었다. 이 세션에서는 자이로센서, 홀 센서, CT 센서, 그리고 두 편의 온도 센서의 판독 회로에 관한 연구들이 발표되었다.

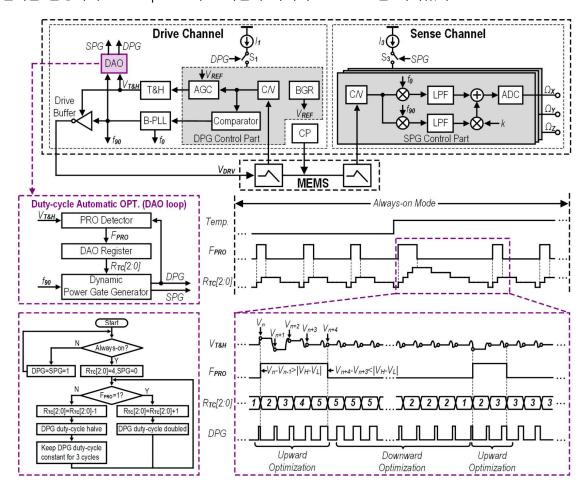

#27-1 Xidian University, Wearable 기기 및 mobile 장치에서 always-on mode로 동작하는 MEMS gyroscope sensor readout에 대한 논문이다. Always-on mode로 동작하는 MEMS gyroscope sensor 는 적용되는 application 특성에 따라 빠른 wake-up time과 저전력 특성을 필요로 한다. 기존 연구에서는 burst-mode PLL (BPLL) 기법을 사용하여 저전력과 빠른 wake-up time을 구현했지만, 온도 변화로 발생하는 parasitic relaxation oscillation (PRO) 현상으로 인해 안정성 문제가 발생한다. 본 논문에서는 duty-cycle automatic optimization (DAO) 기법을 적용한 chip을 180nm BCD 공정으로 제작했으며, PRO 현상에 의한 불안정성을 ±5% 내로 유지하여 안정적인 성능을 달성했다. 또한 three axis system에서 always-on mode의 wake-up time은 2.8ms와 동시에 847nA 수준의 소비전력을 달성하여 wake-up time과 소비전력 사이의 trade-off 를 극복했다.

[그림] #27.1 논문에서 제안하는 duty-cycle automatic optimization (DAO)가 적용된 BPLL-based always-on MEMS gyroscope 시스템의 구조 및 동작.

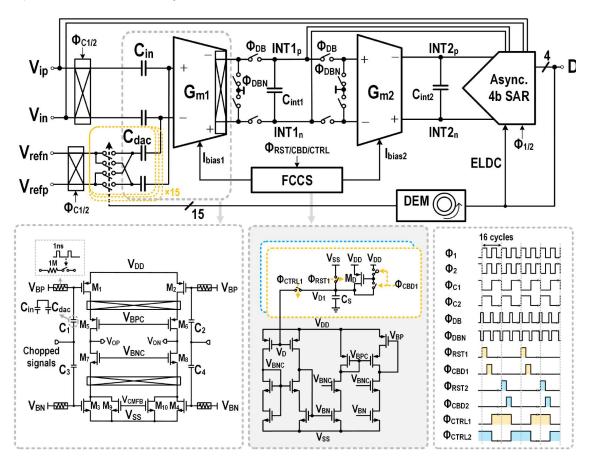

#27-3 Zhejiang University, 본 논문은 IoT application과 low power sensor 시스템을 위한 BW/power의 확장성을 갖는 low noise sensor 인터페이스 회로를 제안했다. 제안하는 회로는 Gm-C ΔΣ modulator (Gm-C CTDSM)와 frequency-controlled current source (FCCS)을 이용하여 연속시간 신호를 처리하며, 기존의 discrete-time ADC 방식과 비교하여 더 낮은 input-referred noise density를 갖는다. 130nm CMOS 공정으로 제작되었으며, 225배의 BW/power 확장성, 46nV/rtHz의 input referred noise density, 85dB의 SNDR을 달성했다.

[그림] #27.3 논문에서 제안하는 current-reuse pseudo-differential amplifier, FCCS operating in a ping-pong mode가 적용된 CT sensor의 전체 system.

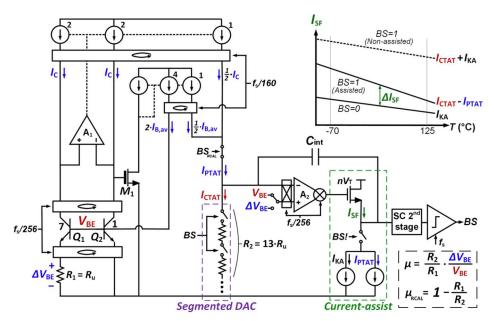

#27-4 TU Delft, Noise-optimized charge-balancing scheme과 current-assisted amplifier를 적용한 BJT-based temperature sensor를 제안했다. 제안하는 temperature sensor는 높은 SNR을 달성하기 위해 noise-optimized charge balancing scheme을 활용했다. 또한 높은 정확도를 위해 segmented DAC를 적용하여 기생 capacitance에 의한 영향을 줄였으며, resistor calibration 기법, chopping 기법과 dynamic element matching (DEM)을 적용하여 mismatch 및 noise로 인한 error를 감소시켰다. 또한, 높은 energy efficiency를 위해 필요한 순간에만 추가적인 current를 제공하는 current-assist technique을 사용했다. 제안하는 회로는  $0.18\mu m$  CMOS 공정으로 제작했으며,  $f_s=50kHz$ 에서 0.79mK,  $f_s=400kHz$ 에서 2.3mK의 해상도를 제공한다. 또한,  $80fJ\cdot K^2$ 의 FoM과  $0.05mm^2$ 의 면적을 달성했다.

[그림] #27-4 논문에서 제안하는 noise-optimized charge-balancing scheme의 구조.

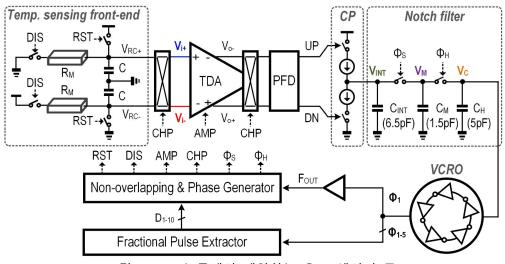

#27-5 University of Macau, Wire-metal 기반 저면적 온도 센서에 대한 논문이다. 제안하는 온도 센서는 fractional-discharge 방식의 frequency-locked-loop (FLL)과 time-domain amplifier (TDA)를 활용하여 온도를 측정한다. Fractional-discharge 기법을 통해 capacitor 방전 시간을 단축하여 큰 면적의 저항을 사용하지 않더라도 정확한 온도 측정이 가능하며, TDA의 chopping 기법을 적용해 DC offset과 1/f noise를 제거했다. 28nm 공정으로 제작했으며, 센서는 -40-125℃ 범위에서 ±0.2℃ (3σ) 이내의 높은 정확도를 유지하며, 45fj·k²의 FoM을 달성하였다. 또한, 28/65nm의 공정 기반 저항형 온도센서 대비, 전력 소모 12배 감소, 면적 2.2배 감소 등의 개선을 이루어 system-on-chip 환경에서의 활용 가능성을 높였다.

[그림] #27-5 논문에서 제안하는 온도 센서의 구조.

## **Session 28: Capacitive Sensor Readout**

ISSCC 2025의 Session 28은 capacitive sensor readout 라는 주제로 총 4편의 논문이 발표되었다. 이 세션에서는  $\Delta\Sigma$  modulation, SAR에 이르는 센서 판독 회로에 관한 연구들이 다수 발표되었다.

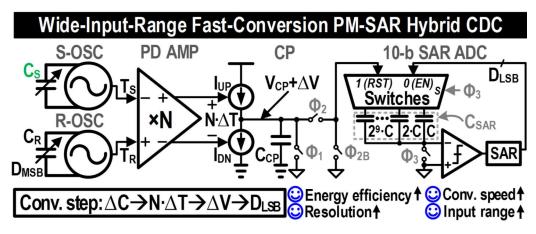

#28-1 KAIST, 넓은 입력 범위와 빠른 변환 속도를 동시에 구현한 PM-SAR hybrid capacitance-to-digital converter (CDC)를 제안한다. 제안하는 CDC는 period-modulation (PM) 방식과 successive approximation register (SAR) 방식을 결합한 하이브리드 구조를 채택하며, 센서 및 기준 캐패시턴스 ( $C_{Sr}$ , $C_R$ )는 발진기 (S-OSC, R-OSC)에 의해 주기 정보 ( $T_{Sr}$ , $T_R$ )로 변환되고, 이 주기의 차이 ( $\Delta T$ )를 period-difference amplifier (PD AMP)가 증폭한 후, charge pump (CP)를 통해  $\Delta T$ 가  $\Delta V$ 로 변환되며, 최종적으로 SAR ADC에서 디지털 값 ( $D_{LSB}$ )로 변환된다. 그 결과, 제안하는 CDC는 65nm 공정에서 제작하였으며, 18.5nF의 입력 범위와  $6.1\mu$ s의 변환 속도 (@18.1pF)를 달성하며, 기존 CDC가 갖는 해상도와 변환 속도 간의 trade-off를 극복하였다. 또한, 138fJ/conv.-step의  $FoM_W$ 와 173.9dB의  $FoM_S$ 를 달성했다.

[그림] #28-1 논문에서 제안하는 PM-SAR hybrid CDC의 구조.

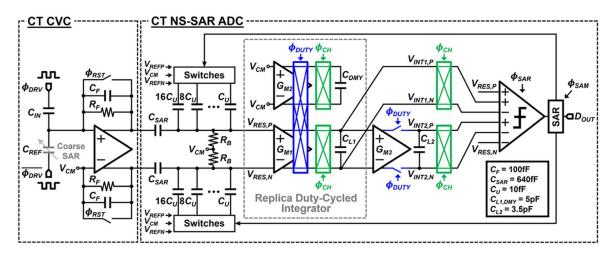

#28-2 KAIST, continuous-time (CT) 도메인에서 highpass (HP) noise-shaping scheme을 적용한 continuous-time noise-shaping SAR capacitance-to-digital converter (CT NS-SAR CDC)를 제안한다. 제안하는 CDC는 continuous-time capacitance-to-voltage converter (CT CVC)를 통해 입력 신호를 전압으로 변환한 후, HP noise-shaping을 적용한 SAR ADC를 이용하여 양자화 한다. 또한, chopper-based CP HP loop filter를 통해 flicker noise를 제거하고 anti-aliasing 기능을 제공하며, replica duty-cycled integrator (RDI)를 적용해 전력 소모를 줄이고, error-charge integration을 방지하여 안정적인 동작을 유지한다. 제안하는 CDC는 0.18μm CMOS 공정으로 제작되었으며, 총 전력 소모 15.2μW (@1.2V supply)에서 189.3dB의 FoM<sub>S</sub>, 14.5fJ/conv.-step의 전력 효율, 17.7aF<sub>rms</sub>의 해상도를 달성했다.

[그림] #28-2 논문에서 제안하는 CT CVC와 CT NS-SAR ADC의 구조.

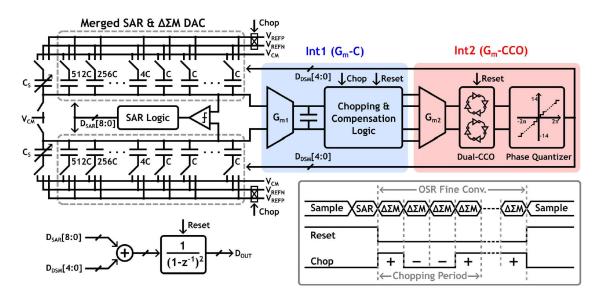

#28-3 Peking University, Chopping 기반 kT/C 노이즈 제거 기법과 add-then-subtract phase-domain lead-compensation technique을 적용하여 고해상도와 높은 에너지 효율을 달성한 capacitance-to-digital Converter (CDC)를 제안하였다. 또한,  $2^{nd}$ -order incremental-zoom 아키텍쳐를 적용하여 저전력으로  $8.7aF_{rms}$ 의 캐패시턴스 측정을 가능하게 한다. 제안하는 CDC는 28nm CMOS 공정에서 제작되었으며,  $70.1\mu$ W의 전력을 소비하면서 93.8dB의 SNR을 달성하였다. 기존 방식보다 더 낮은 샘플링 노이즈를 가지며,  $10.4\mu$ S의 측정 시간 내에서도 높은 정확도를 유지하다. 특히,  $FoM_S$ 이 185.2dB로  $100\mu$ S 이하의 측정 시간을 가지는 기존 CDC 중에서 최고 성능을 달성하였다.

[그림] #28-3 논문에서 제안하는 incremental-zoom CDC의 구조 및 timing diagram.

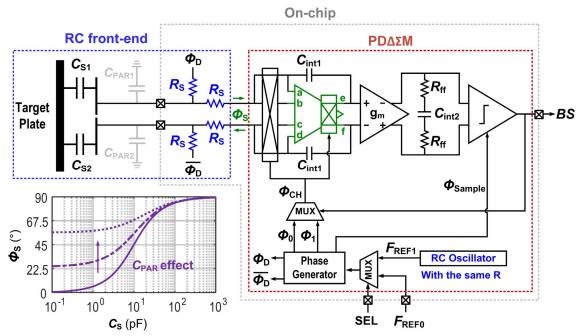

#28-4 Tsinghua University Differential RC front-end와 phase-domain-delta-sigma modulator (PDΔΣM)을 적용하여 높은 정확도를 갖는 capacitive displacement sensor를 제안한다. 센서는 floating target 환경에서도 안정적으로 동작할 수 있도록 differential RC front-end를 통해 sensing capacitance를 phase shift로 변환한 후, 이를 PDΔΣM을 이용해 bitstream으로 변환하여 displacement 정보를 digital output으로 출력하는 구조를 갖는다. 또한, feedforward-compensated two-stage opamp를 적용함으로써 input impedance를 최소화하여 phase-sensing error를 줄였으며, 기준 주파수 (F<sub>REF</sub>)의 온도 변화 영향을 최소화하기 위해 temperature coefficient (TC)가 매칭된 resistor와 capacitor를 사용하여 TC accuracy를 개선하였으며, chopping과 notch-filtering을 통해 DC offset과 low-frequency noise를 제거하고 output frequency jitter를 감소시켜 센서의 안정성을 높였다. 제안하는 CDC는 0.18μm 공정으로 제작되었으며, 143dB 이상의 dynamic range, 21.3aF<sub>rms</sub>의 resolution, 119dB의 CMRR (@DC)을 달성하였다.

[그림] #28-4 논문에서 제안하는 RC front-end와 PD $\Delta$ ΣM의 구조.

## 저자정보

## 김종석 교수

● 소 속 : 한양대학교 ERICA 전자공학부

• 연구분야 : Display circuit, sensor circuit, biomedical circuit

• 이 메 일 : jskim383@hanyang.ac.kr

● 홈페이지: https://www.SIDLAB.net

# 2025 International Solid-State Circuits Conference

# (ISSCC) Review

연세대학교 시스템반도체공학과 박관서 교수

**Topic: Wireline (1)**

## Session 7: Ultra-High-Speed Wireline

이번 ISSCC2024의 Session 7은 Ultra-High Speed Wireline이라는 주제로 총 10편의 논문이 발표되었다. 이 세션에서는 초고속 유선통신을 위한 송수신기 개발에서 데이터 속도와 에너지 효율을 높이는 것에 중점을 두었고 고성능 클록 복원 및 생성에 대한 논문들도 발표되었다.

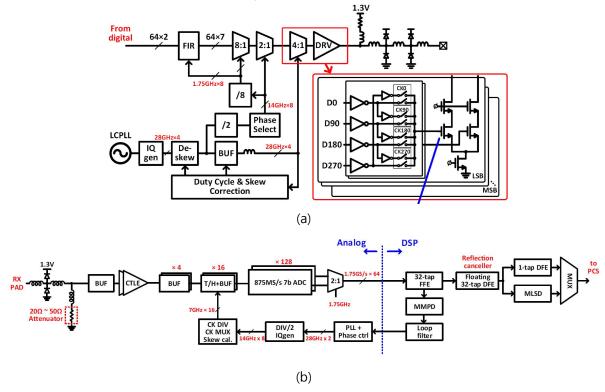

#7-1 Mediatek, 본 논문은 DSP기반의 초고속 송수신기에 대한 발표이고 4nm FinFET에서 구현하였다. 212.5Gb/s의 동작속도를 가지고 50dB 이상의 채널 손실을 보상하며 2.5E-6 BER을 달성하는 완성도 높은 PAM-4 송수신기를 개발하였다. 그림 1(a)과 같이 송신기는 CML 기반의 7b DAC을 활용한 driver를 구현하였고 측정 결과 98.5의 RLM과 35.5dB의 SNDR을 달성하였다. 수신기는 그림 1(b)와 같이 T-coil, source follower buffer, CTLE로 AFE를 구성하고 28GS/S의 T/H buffer와 7b 875MS/s SAR ADC로 아날로그 회로를 구성하고 DSP에서는 32-tap FFE, floating 32-tap DFE, MLSD, MMPD 등으로 구성하였다. 송수신기 시스템에 클록 공급을 위한 jitter-cleanup PLL이 있고 각TX/RX에 PLL을 두어 클록킹을 구현하였다. 송수신기 테스트 결과, 40dB, 50.5dB 채널 손실에서 1E-10, 2.5E-6 BER을 달성하고 레인당 5.3pJ/b의 에너지 효율을 달성하였다.

[그림 1] 송수신기의 전체적인 구조를 보여주는 블록 다이어그램 (a) 송신기 (b) 수신기

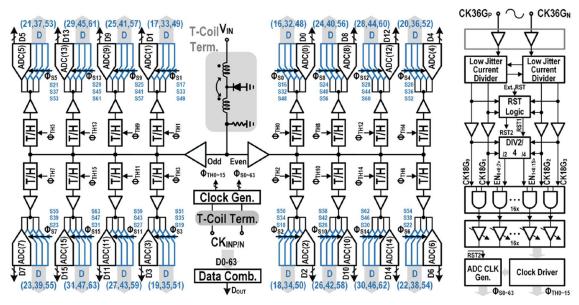

#7-2 Marvell, 본 논문은 5nm FinFET에서 개발한 212.5Gb/s의 동작속도를 가지고 46dB loss까지 보상이 가능한 Long reach용 송수신기에 대한 발표이다. 200Gb/s 이상의 고성능 송수신기를 저전력으로 구현하는 것을 목표로 한 논문이다. 송신기는 그림 2(a)와 같이 구현되었고 10-tap FIR filter 기반의 digital equalization과 8b DAC 기반의 driver를 포함한다. LC PLL로부터 28GHz 클록이 생성되고 resonant CML stage를 이용하여 클록을 분배하여 clock jitter를 개선한다. Duty cycle, quadrature error, skew 등의 클록킹 회로 성능을 개선하는 기법들이 추가되었다. 저전력 구현을 통해 0.86pJ/b의 에너지 효율을 달성하였다. 수신기는 그림 2(b)와 같이 구현되었고 파워 및 잡음에 효율적인 AFE 구현과 저잡음 클록킹 기술들을 포함한다. AFE는 T-coil, 2-stage CTLE, 112-way TI-ADC로 구성된다. Scalable SAR supply/resolution/DR/sub-ADC count를 이용하여 저전력의 SAR ADC를 구현하였으며 offset/gain/timing skew 등의 비이상적 동작에 대한 디지털 보정회로를 탑재하였다. DSP에서는 29-tap FFE와 1-tap speculative DFE를 포함하며 MLSD를 적용하였다. 측정 결과, 송신기는 212.5Gb/s에서 36.1 dB 이상의 SNDR과 0.97의 RLM, 73fs RJ의 clock jitter를 달성하였다. 수신기는 33dB에서 3E-10, 46dB에서 6E-9의 BER을 달성하였다. 최종적으로 송수신기 합쳐서 2.2pJ/b의 에너지 효율을 달성하여 굉장히 좋은 성능을 얻었다는 점이 인상 깊은 논문이다.

[그림 2] 송수신기의 전체적인 구조를 보여주는 블록 다이어그램 (a) 송신기 (b) 수신기

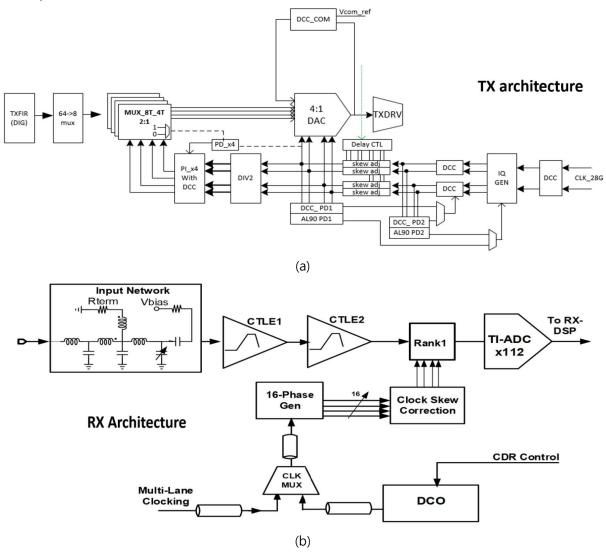

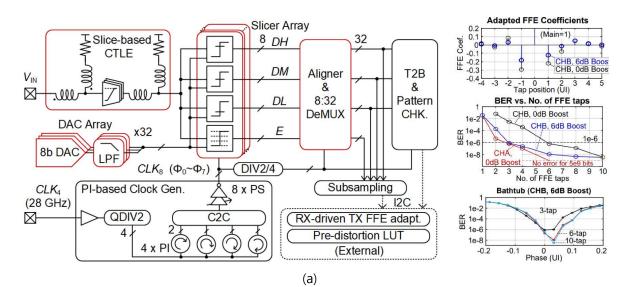

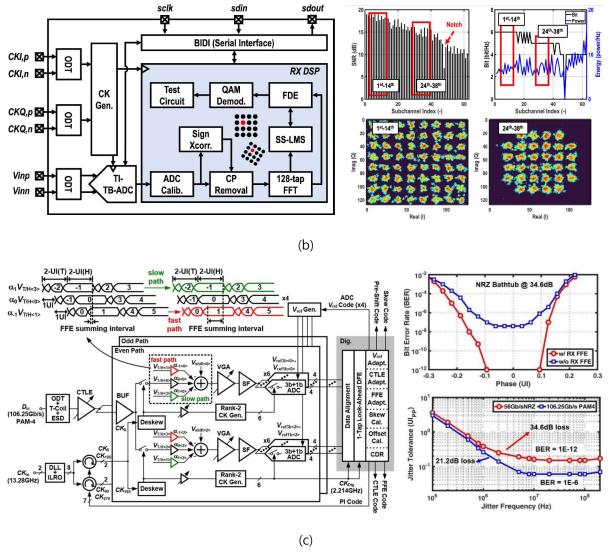

#7-3 Peking University, 7-5 DGIST, 7-6 National Tsing Hua University, 100Gb/s 이상급의 수신기 연구를 세 개의 대학교 연구그룹에서 발표되었다. 우선, 그림 3(a)와 같이 224Gb/s PAM-4 수신기를 XSR 어플리케이션을 타겟하여 12nm 공정에서 개발하였다. Slice-based CTLE 를 구현하였고 group delay 를 최적화하여 59GHz 의 3dB bandwidth 를 달성하였다. 8-way interleaving 을 통하여 샘플링을 하였고 phase 당 3 개의 data level 과 1 개의 error level 을 활용하였다. PI 기반의 clock generator를 활용하여 파워와 면적 효율적으로 설계하였고 INL 이슈를 해결하기 위해 pre-distortion 기술을 적용하였다. 그 결과, 224Gb/s 의 동작속도와 13.6dB 채널 손실에서 3-tap TX FFE 만 활용하여 8.1E-7 의 BER 을 달성하였고 1.11pJ/b 의 좋은 에너지 효율을 달성하였다. 다음으로, 그림 3(b)와 같이 112Gb/s multitone wireline receiver 를 5nm 공정에서 구현하였다. 기존의 SAR ADC 기반의 초고속 PAM-4 수신기를 대신하여 time-based ADC 를 활용하고 discrete multitone modulation 기법을 적용한 초고속 수신기를 개발하였다. 제안하는 방식은 PAM-4 기반의 송수신기에서 발생할 수 있는 frequency response 의 ripple, notch 등의 문제점을 개선할 수 있다. 아날로그 회로는 64-way time interleaved TB ADC 와 면적 및 파워를 최소화하기 위한 shared injection-locked ROSC 를 포함한다. TB ADC 로 샘플링된 데이터는 DSP 에서 처리되며 CP location 을 찾기 위한 sign-sign cross-correlation 기반의 감지 기능이 있고 multi-path delay feedback 구조를 가지는 128-tap FFE 와 frequency domain equalizer 도 탑재하였다. 그 결과 52GS/S 속도에서 5.4bit 의 ENOB 를 달성하고 DNL 최대 0.31LSB, INL 최대 1.03LSB 를 얻었다. 또한, 112.5Gb/s 의 동작속도, 18dB 의 insertion loss 에서 4E-4 의 BER 과 3.14pJ/b 의 에너지 효율을 달성하였다. 마지막으로, 그림 3(c)와 같이 3-tap FFE 와 1-tap speculative DFE 를 탑재한 106.25Gb/s 의 PAM-4 수신기를 구현하였다. FFE 를 통해 1+05D pulse shaping 을 하여서 8 개의 slicing level 을 이용하여 speculative PAM-4 data 를 복원하였다. 또한, fast/slow path 와 pre-shift circuit 을 이용하여 성능을 높였고 lock ahead DFE 와 1+0.5D baud-rate PD 를 활용하여서 완성도를 높였다. 그 결과 106.25Gb/s PAM4 데이터를 복원하는데 1E-6 의 BER 을 달성하였고 2.06pJ/b 의 에너지 효율을 얻었다.

[그림 3] (a) 224Gb/s PAM-4 수신기 블락도 및 측정결과, (b) 112Gb/s DMT 수신기 블락도 및 측정 결과, (c) 106.25Gb/s PAM-4 수신기 블락도 및 측정 결과

## 저자정보

## 박관서 교수

● 소 속 : 연세대학교 시스템반도체공학과

● 연구분야 : High Speed I/O

• 이 메일: kwanseo@yonsei.ac.kr

● 홈페이지 : aics.yonsei.ac.kr

# 2025 International Solid-State Circuits Conference

# (ISSCC) Review

광운대학교 전자통신공학과 채주형 교수

**Topic: Wireline (2)**

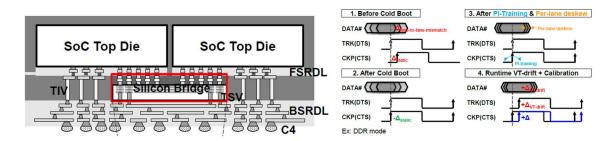

## Session 22: Memory Interface

이번 ISSCC 2025의 Session 22는 Memory Interface의 주제로 총 5편의 논문이 발표되었다. 모두한국에서 발표된 논문으로 22-2 논문은 HBM에서의 Quadrature Clock Distribution을 위한 주제이며, 나머지 4개의 논문은 모두 Single-Ended Multi-Level Signaling을 위한 다양한 아이디어를 제안하였다.

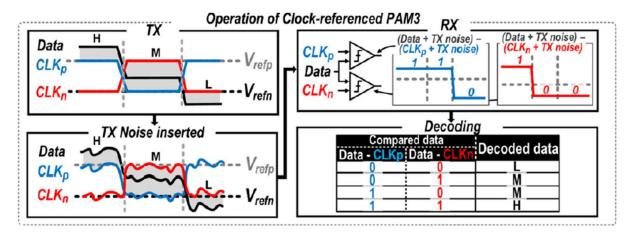

#22-1 SNU, 본 논문은 Chiplet과 Short-Reach Memory Interface를 위한 Clock-Referenced PAM-3 (CR-PAM3) Tranceiver를 제안하였다. Single-Ended Signaling이 가지는 Voltage Reference (Vref) Offset과 TX/RX 간의 VDD와 Vref 노이즈 성분이 Uncorrelate되는 문제를 해결하기 위하여 Clock 신호를 RX의 Vref로 활용하는 방법을 제안하였다. 이와 함께 Far-End Crosstalk (FEXT) Cancellation 기법 또한 제안하였다. 이를 통해 Supply Noise가 있는 환경에서도 42 Gb/s/pin 속도에서 10<sup>-12</sup> 이하의 BER 성능을 달성할 수 있었으며, 0.275 pJ/bit의 에너지 효율을 달성하였다.

[그림 1] 제안하는 CR-PAM3의 핵심 동작.

#22-3 SK Hynix, 본 논문은 Hybrid DFE가 적용된 GDDR7 PAM3 Receiver를 제안하였다. GDDR7은 PAM3 방식 적용과 함께 데이터 전송속도의 증가로 ISI를 제거하기 위한 DFE가 RX에 필요하다. 이 때 Direct DFE는 Feedback Time의 이슈가 있으며, Loop-Unrolled DFE는 파워 및 면적 증가의 이슈가 있다. 이를 해결하기 위하여 Short Transition에는 Direct DFE를 적용하고, Long Transition에

는 Loop-Unrolled DFE 적용하는 Hybrid DFE 방식을 제안하였다. 이를 통해 모두 Direct DFE만을 사용하는 경우에 비해 20%의 Feedback Time이 감소되었으며, -5 dB 손실의 GDDR7 채널 환경에서 42 Gb/s/pin의 데이터 수신성능을 달성하였다.

[그림 2] Hybrid-DFE PAM3 Receiver의 블록다이어그램과 동작 원리.

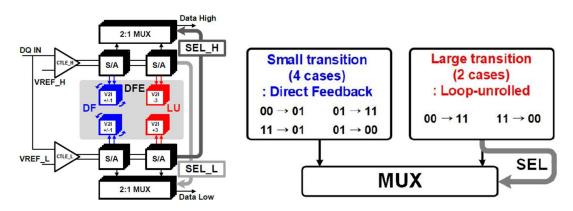

#22-5 Korea University, 본 논문에서는 Receiver DFE의 Feedback Time 및 파워/면적 문제와 Current Integrator의 Common-Mode Degradation 문제 등을 해결할 수 있는 Capacitive Feedback Equalizer (CFE)를 제안하였다. Current Integrator에 Capacitor를 결합하여 1-UI 이전의 데이터를 인가함으로써 Delay-less Equalizer를 구현하면서 Common-Mode 전압 또한 증폭시켰다. 이를 통해 0.3 pJ/bit의 에너지 효율로 32 Gb/s PAM4 데이터의 수신성능을 달성하였다.

[그림 3] 제안하는 Capacitive Feedback Equalizer의 동작 원리

## Session 36: Ultra-High-Speed D2D and High-Performance Optical Tranceivers

이번 ISSCC 2025의 Session 36에서는 총 9편의 논문이 발표되었으며 이 중 3편의 Die-to-Die (D2D) Interface 논문과 6편의 Optical Interface 논문으로 구성되었다. 이 중 D2D Interface는 2편의 UCle Advanced Package Link가 소개되었으며, 1편은 Edge Density를 늘리기 위한 Simultaneous Bidirectional Signaling 기법이 적용된 논문이 발표되었다. 3편 모두 Edge Density를 높이는 것에

#36-1 TSMC, 36-3 Cadence 이번 ISSCC에서는 2개의 UCle Advanced Package Link 논문이 소개되었다. TSMC의 경우 Dynamic Clock Gating을 적용하여 전력 소모를 감소시키면서 모드 변경 시점에서의 Voltage Droop 문제를 해결하기 위한 여러 방안들을 제안하였다. 이를 통해 64 Lane에서 32 Gb/s/pin의 특성을 달성하였으며, 또한 45 um의 Bump Pitch에서 10.5 Tb/s/mm의 Edge Density의 성능을 달성하였다. Cadence의 경우 CoWoS Packaging을 활용하였으며 이를 통해 16 Gb/s/pin의 전송 성능과 45 um의 Bump Pitch에서 5.27 Tb/s/mm의 Edge Density의 성능을 달성하였다.

[그림 4] UCIe System Overview와 RX Deskew Calibration 동작.

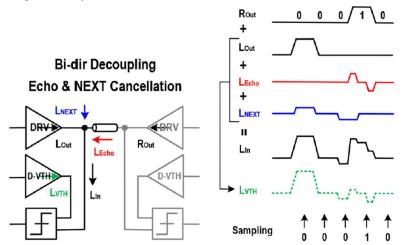

#36-2 Peking University, 본 논문은 D2D Interface의 Edge Density를 증폭시키기 위하여 Simultaneous Bidirectional (SBD) Signaling을 적용하였다. 채널간 피치가 작은 D2D Interface 환경에서 SBD를 적용하기 위해서는 Bi-Directional Coupling, NEXT, FEXT, 그리고 Echo 등의 노이즈를 줄여주는 것이 필요하며 본 논문에서는 이를 위한 방법을 제안하였다. FEXT의 경우 Capacitive/Inductive Coupling의 양이 동일하도록 채널을 디자인하여 노이즈의 영향을 최소화하였으며, NEXT, Echo 및 Bi-Directional Coupling은 Dynamic Voltage Threshold를 사용한 데이터 샘플 링을 적용하여 문제를 해결하였다. 이를 통해 64 Gb/s/wire의 데이터 전송 성능을 달성하였으며 10.5 Tb/s/mm의 Edge Density 특성을 얻었다.

[그림 5] Dynamic Voltage Threshold를 이용한 SBD 데이터 샘플링.

# 저자정보

# 채주형 교수

● 소 속 : 광운대학교 전자통신공학과

● 연구분야 : High Speed I/O, In-Memory Computing

• 이 메 일 : jhchae@kw.ac.kr

● 홈페이지: https://sites.google.com/view/jhchae

# 2025 International Solid-State Circuits Conference

# (ISSCC) Review

숙명여자대학교 전자공학전공 정준원 교수

Topic: Power (1)

## Session 9: Ubiquitous Power Delivery

Session 9에서는 효율 향상, 출력 전력 증가, 과도 응답 속도 개선, 소형화를 목표로 하는 다양한 기술이 발표되었다. 주요 발표 내용은 AC-DC 변환기, 공급 변조기 (Supply Modulator), LDO, 무선 전력 송수신기, 하이브리드 변환기에 관한 것이다.

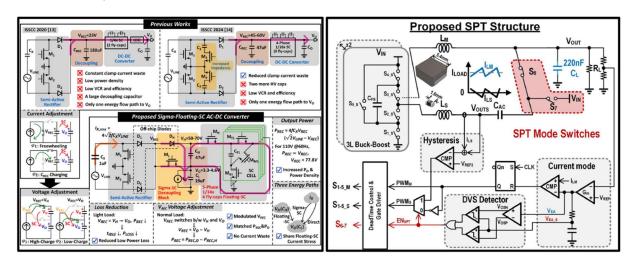

[그림 1] (좌) <#9.1> Sigma-floating-SC AC-DC 변환기, (우) <#9.4> Ripple cancellation SPT

- #9-1 University of Macau에서 IoT와 smart home device 용 고효율 AC-DC converter를 소개했다. Sigma-floating-SC AC-DC 변환기를 제안하여 direct charging path를 추가했다. 이를 통해 current freewheeling을 완화하여 8%의 효율 향상을 얻었다. 82 ~ 230 V AC 전압을 입력 받아 3.3 ~ 4.6 V DC 전압을 출력한다. 최대 출력 전력은 1.52 W이며 최대 효율은 81.3% 이다.

- #9-4 University of Science and Technology of China에서는 5G NR power amplifier를 위한 symbol-power-tracing (SPT) supply modulator를 발표했다. Ripple cancellation 기법을 적용하여 secondary converter가 main converter의 인덕터 전류 리플을 상쇄하도록 설계되었다. 이로 인해 로드 커패시터를 220 nF, 출력 전압 리플을 12 mV로 저감하였으며, 102 ns/V의 up transition 및 180 ns/V의 down transition을 달성했다.

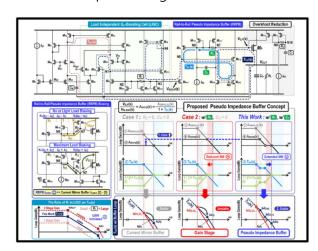

- #9-5 서강대학교에서 Sub-1V analog LDO 기술을 발표했다. Rail-to-rail pseudo impedance buffer 와 load-independent Gm-boosting cell을 제안하여 넓은 로드 범위 (0 A  $\sim$ 1.2 A), 넓은 입력 범위 (0.7 V  $\sim$  1.4 V), dropout 범위 (0.05 V  $\sim$  0.2 V)에서 phase margin을 확보했다. 부하 전류가 커질수

록 감소하는 phase margin을 보상하는 피드백 루프가 추가되었다.

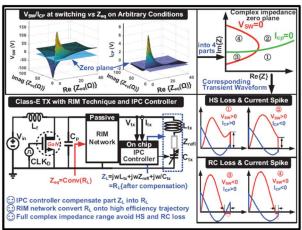

[그림 2] (좌) <#9.5> Sub-1V analog LDO, (우) <#9.7> Class-E transmitter

#9-7 Xi'an JiaoTong University에서 무선 전력 송수신을 위한 Class-E transmitter를 소개했다. Adaptive real-part impedance-matching (RIM) 기술과 imaginary-part phase compensation (IPC) 기술을 제안하여 스위칭 손실을 줄이고, 스위칭 타이밍을 최적화하였다. 3 W~29 W의 로드 범위에서 88% ~ 94.2%의 높은 효율을 달성하였다.

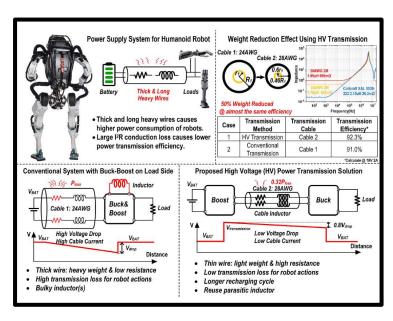

#9-9 University of Macau에서 휴머노이드 로봇용 power transmission cable을 위한 bi-directional dual-path boost-48 V-buck hybrid converter를 발표했다. 전력 송신부에서 승압, 전력 수신부에서 감압하여 transmission cable에서 발생하는 전력 손실을 저감했다. 이를 통해 transmission cable의 무게를 줄이고, 96.7% (16.5 W)의 높은 효율을 달성하였다. Cable의 기생 인덕터 성분을 재사용하였다.

[그림 3] <#9.9> 휴머노이드 로봇용 bidirectional hybrid 변환기

## Session 31: Energy Harvesting and IoT Power

Session 31 에서는 에너지 하베스팅 및 IoT 기기의 전력 관리(PMIC)를 위한 4 편의 논문이 발표되었다. 특히 효율 향상과 경량화를 목표로 하는 3 편의 Piezoelectric 에너지 하베스팅 기술과 1 편의 mm-scale IoT PMIC 기술이 소개되었다.

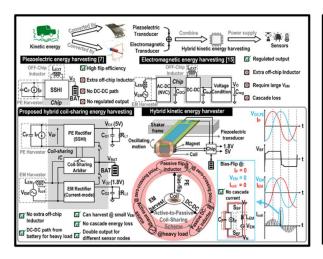

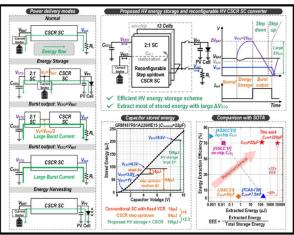

[그림 4] (좌) <#31.1> Hybrid energy harvesting system, (우) <#31.4> HV SC 변환기

#31-1 Delft University of Technology 에서는 Fully-Integrated 하이브리드 에너지 하베스팅 시스템을 발표했다. Piezoelectric 및 Electromagnetic (EM) energy harvester 를 통합하여 단일 시스템에서 두 가지 에너지원 활용이 가능하도록 설계되었다. 또한 EM 코일을 공유하여 bias-flip, DC-DC 변환, 및 EM 에너지 추출을 수행하는 구조를 제안하였다. 기존 방식 대비 외부부품(인덕터, 커패시터)을 제거하여 소형화에 성공했으며, 2.72 mW 의 출력 전력 및 90%의 변환효율을 달성했다.

#31-4 University of Macau 에서는 mm-scale IoT 기기를 위한 capacitive PMIC를 발표했다. 고전압 (HV)으로 스토리지 커패시터를 충전 후, 온칩 Switched-Capacitor (SC) 변환기를 통해 에너지를 방출하는 방식을 제안하였다. 이를 통해 기존 방식 대비 35 배 높은 Energy Extraction Efficiency (EEE)와 27 배 증가한 Burst Energy 전달이 가능하며, 최대 5.68 mJ 의 Burst Energy 및 71%의 EEE를 기록했다. 또한 스토리지 커패시터의 크기를 기존 대비 34 배 저감하여 소형화에 기여했다.

## 저자정보

## 정준원 교수

● 소 속 : 숙명여자대학교 전자공학전공

• 연구분야 : Sensor Readout ICs / Power Management ICs

• 이 메 일 : jwjeong@sookmyung.ac.kr

• 홈페이지: https://sites.google.com/sookmyung.ac.kr/csl

# 2025 International Solid-State Circuits Conference

# (ISSCC) Review

성균관대학교 반도체융합공학과 조건희 교수

Topic: Power (2)

## Session 21: Compute and USB Power

이번 ISSCC 2025의 Session 21은 Compute and USB Power 라는 주제로 총 9편의 논문이 발표되었다. 이 세션에서는 다양한 power management IC (PMIC) 분야에서 높은 효율과 작은 폼 팩터를얻기 위한 기술 뿐만 아니라 여러 phase 동작에서도 전압 및 전류의 밸런싱을 맞추기 위한 기술들이 소개 되었다.

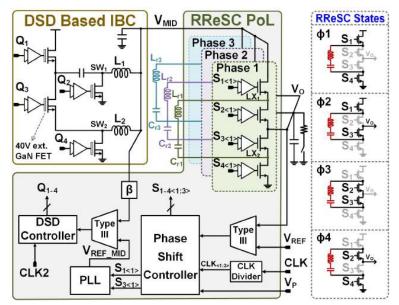

#21-1 은 중국 저장대학교에서 발표한 논문으로써, AI 및 고성능 컴퓨팅(HPC) 수요 증가에 따른 고효율 전력 변환 솔루션을 제안한다. 최근 컴퓨팅 전력 요구가 급증하면서, 더 높은 전력 용량, 효율 및 빠른 응답 속도를 갖춘 전력 공급 시스템이 필수적이며, 이를 위해 다수의 Point-of-Load (PoL) 컨버터가 병렬로 동작하지만, 다중 위상(phase) 컨버터에서 높은 효율을 유지하기 위해서는 정밀한 전류 밸런스 제어가 필요하다. 본 논문에서는 고효율 12V-to-1V 전력 변환기를 위한 two-stage 구조를 제안하였다. 첫 번째 stage 에서는 12V에서 1.8V로 변환하는 Double-Step-Down (DSD) 컨버터를 적용해 높은 변환 효율과 넓은 변환 비율(conversion ratio)을 확보하였으며, 두 번째 stage에서는 1.8V에서 1V로 변환하는 3-phase 동작의 Regulated Resonant Switched-Capacitor Converter (RReSC) 구조를 도입해 높은 전력 밀도(power density), 고효율 및 빠른 과도 응답 (transient response)을 달성하였다. RReSC는 위상 이동 제어(phase-shift control)를 활용해 고효율 상태에서 동작하며, 부하 변화 시 빠르게 부스트(Boost) 또는 벽(Buck) 모드로 전환해 26mV의 낮은 전압 강하(undershoot)를 실현하였다. 제안된 컨버터는 PoL 변환기의 최대 효율 96.0%, 시스템 전체 효율 89.3%를 달성했으며, 고속 동적 전압 스케일링(DVS)과 우수한 부하 대응 성능을 보여 주었다.

[그림 2] 21.1에서 제안한 12-to-1V resonant 기반의 two-stage converter

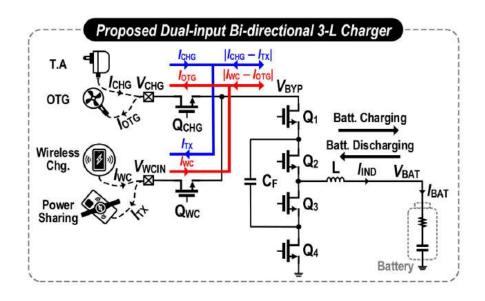

#21-2 삼성전자에서 발표한 논문이다. 이 논문에서는 듀얼 입력을 지원하는 3-Level 배터리 충전 기 기술을 소개한다. 기존 3-Level Buck 컨버터 구조를 기반으로 유선 및 무선 충전 입력을 동시에 수용할 수 있도록 설계되었으며, 유선 입력 단자는 유선 충전 및 On-The-Go (OTG) 모드, 무선 입력 단자는 무선 충전 및 전력 공유 기능을 제공한다. 또한, bi-directional 동작 환경에서도 빠른 VCF(플라잉 커패시터 전압) 균형을 유지하기 위해 coarse-fine VCF balancer 기술을 제안하여, 방향과 관계없이 안정적인 전압 균형을 확보하였다. 아울러, 주파수 폴드백(frequency foldback) 제어를 적용해 넓은 전압 변환 비(VCR)를 구현함으로써, 경부하 및 고부하에서도 높은 충전 효율을 유지할 수 있도록 설계되었다.

[그림 2] 21.2에서 제안한 dual-input bi-directional 3-level charger

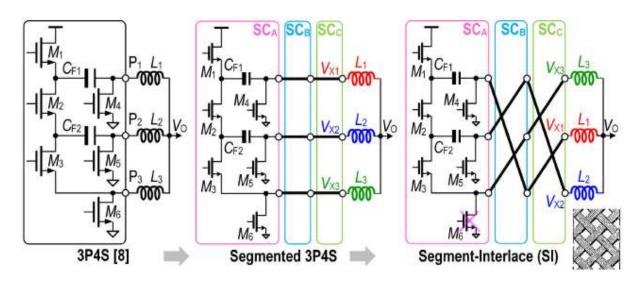

#21-3 중국 마카오대학에서 발표한 논문이다. 데이터센터에서 12V 입력을 직접 변환하는 multiphase (MP) 컨버터는 증가하는 컴퓨팅 성능 요구에 대응하지만, 부하 변화 시 출력 전압 저하를 줄이기 위해 인덕터 전류(IL) 상승 속도를 높이는 것이 중요하다. 기존 MP 컨버터는 위상 간 듀티사이클 차이로 인해 IL 불균형이 발생하며, 이를 보정하기 위한 추가적인 센싱과 제어 회로가 필요하다. 본 연구에서는 3P4S 구조를 기반으로 한 segmented-interlacing (SI) 컨버터를 제안하여, IL 자동 균형 유지와 동시에 duty 중첩을 허용해 IL 상승 속도를 증가시켰다. 이를 통해 부하 변동시 전압 강하를 92mV로 감소시키고, light-load 시 스위칭 주파수 조절을 통해 효율을 향상시켰다. 제작된 칩은 0.18µm BCD 공정으로 구현되었으며, 최대 92.9% 효율을 달성하며 기존 연구 대비 IL 균형성과 응답 속도를 개선하였다.

[그림 3] 21.3에서 제안한 3P4S에서부터 Segment-Interlacing 컨버터까지의 변천사

## Session 32: Isolated Power and Gate Drivers

이번 ISSCC 2025의 Session 32은 Isolated Power and Gate Drivers 라는 주제로 총 6편의 논문이 발표되었다. 이 세션에서는 전기자동차 및 산업용 반도체와 같은 열악한 환경에서 안정성과 신뢰성을 보장하는 여러가지 기술에 대해 소개하였다. 특히나 높은 변환 효율, 낮은 EMI, 정밀한 게이트 구동기술에 대해 발표하였다.

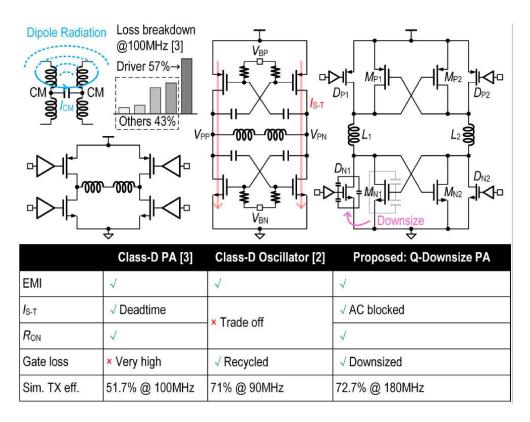

#32-1 마카오대학에서 발표한 논문이다. 본 논문에서는 Q-downsize Class-D 전력 증폭기(PA) 기반의 180MHz 절연형 DC-DC 컨버터를 제안하여, EMI 저감 및 높은 전력 변환 효율(PCE) 유지를 얻고자 하였다. 기존 Class-D 오실레이터의 Shoot-Through Current 문제를 해결하기 위해, cross coupling 된 MOS pair 와 소형 active switch를 결합한 구조를 적용하였다. 이를 통해 PCE를 기존 대비 향상시키고, 높은 주파수(180MHz)에서도 안정적인 동작을 보장하였다. 또한, 스위칭 주파수(f<sub>sw</sub>)와 오실레이션 주파수(f<sub>osc</sub>)의 불일치에도 높은 효율을 유지할 수 있도록 설계하여 EMI 성능

을 개선하였다. 실험 결과, 최대 45.3%의 PCE와 1W의 출력 전력을 달성하였으며, CISPR-32 Class-B EMI 인증 요건을 충족하였다.

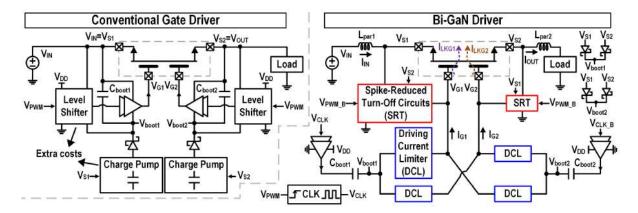

[그림 4] Class-D PA, Class-D oscillator, 제안한 Q-downsize PA 비교

#32-6 대만 National Yang Ming Chiao Tung University에서 발표한 논문이다. 본 논문에서는 48V 전기자동차 전력 시스템용 양방향 GaN load switch (BLS)를 제안하여 역전류 차단 및 과도 전류 (inrush current) 보호 기능을 강화하였다. 기존 back-to-back 스위치 방식 대비 Bi-GaN (Monolithic Bidirectional GaN) 구조를 적용하여 R<sub>ON</sub>을 줄이고, 높은 효율을 유지하도록 설계되었다. 또한, soft start 및 spike reduced turn-off circuit (SRT) 기술을 도입해 전력 스위치의 안정성을 높이고 과전류 및 과전압 문제를 해결하였다. 측정 결과, Bi-GaN 기반 BLS는 11.2mΩ의 낮은 R<sub>ON</sub>을 유지하면서 최대 48V 전압과 25A 전류에서 동작 가능하며, inrush current를 91.4%, overshoot를 89.5% 감소시키는 성능을 보였다.

[그림 5] 기존 gate driver 및 제안한 Bi-GaN gate driver 비교

# 저자정보

## 조건희 교수

소 속 : 성균관대학교 반도체융합공학과

• 연구분야 : Power management ICs, High-voltage gate drivers

• 이 메일: kunhee@skku.edu

• 홈페이지 : https://sites.google.com/view/ecslab

# 2025 International Solid-State Circuits Conference

# (ISSCC) Review

숭실대학교 전자정보공학부 황영하 교수

## **Topic: Data Converter**

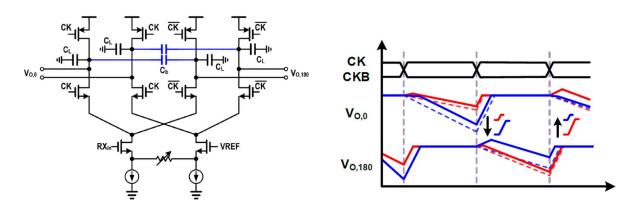

ISSCC 2025의 Session 18은 Noise-Shaping (NS) and SAR-Based ADCs 라는 주제로 NS SAR ADC 2 편, DSM 1편, NS Pipelined ADC 2편, Pipelined ADC 2편 및 극저온 SAR ADC 1편의 논문을 포함하여 총 8편의 논문이 발표되었다. Session 24는 High-Frequency ADCs를 주제로 Time-domain ADC 2편, Pipelined 및 TI Pipelined ADC 5편, TI SAR ADC 1편을 포함하여 총 8편의 논문이 발표되었다.

## Session 18: Noise-Shaping and SAR-Based ADCs

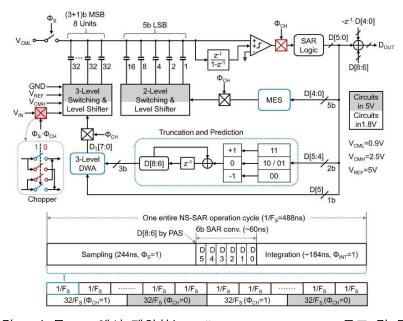

#18-1 중국 UESTC 대학에서 1 kHz BW 기준 189 dB의 높은 Schreier FoM을 갖는 Fully dynamic NS SAR ADC 구조를 제안하였다. 전체 구조는 1차 NS, 8-bit Capacitive DAC (CDAC)에 1차 mismatch error shaping (MES), OSR = 1000 으로 정하여 CDAC mismatch 가 있어도 125 dB 이상의 SNDR, -134 dB 이하의 THD를 달성할 수 있도록 설계하였다. CDAC는 3-level switching에 predict and skip scheme을 적용하여 2-level switching을 쓴 경우와 비교하여 평균 switching energy를 절반으로 줄였으며, CDAC mismatch로 인한 nonlinearity error를 줄이기 위해서 3-bit MSB DWA와 5-bit LSB MES [1]를 결합하였다. 또한 system-level chopping을 적용하여 Vcm error로 인한 in-band even harmonic tone들과 offset 및 1/f noise의 영향을 줄였다. 1차 NS loop에는 floating inverter amplifier 기반 integrator를 적용하여 fully dynamic operation을 달성하였다. Input sampling switch는 5V 소자를 사용하여 differential input swing 범위를 +/-4.7 V로 크게 설계하였다. 이러한 기법들을 바탕으로 180nm 공정에서 제작하여 1 kHz BW에서 120 dB SNDR을 달성하였으며, 189 dB의 높은 Schreier FoM을 기록하였다.

[그림 1] 논문 18.1에서 제안하는 Fully Dynamic SAR ADC 구조 및 동작

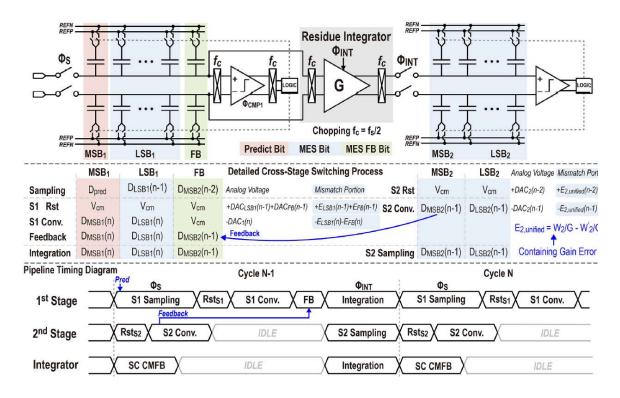

#18-3 중국 북경대에서 Calibration 없이 93.3 dB의 높은 SNDR을 갖는 NS Pipelined-SAR ADC 구조를 발표하였다. Conventional pipelined-SAR 구조의 경우 CDAC mismatch와 residue amplifier의 gain error로 인해 선형성이 저하되는 문제가 있는데, 제안하는 cross-stage gain-mismatch error shaping (GMES) 기법은 gain과 mismatch error를 통합하여 같이 1<sup>st</sup>-order error shaping 하는 방식으로 이러한 문제를 해결하였다. 기존 MES 기법은 이전 bit로 CDAC을 preset 했다가 리셋하기때문에 입력 신호 범위가 감소하는 단점이 있는데, 제안하는 구조에서는 입력 신호 sampling 할때 comparator로 MSB 1 bit을 미리 prediction 및 level shifting 하여 입력 신호 범위가 줄어드는 것을 보상하였다. 또한 현재의 입력 전압을 증폭하여 voltage를 drive하는 residue amplifier 대신에 이전의 residue 전압을 누적하는 integrator 구조를 적용함으로써 1<sup>st</sup>-order quantization noise shaping을 구현하였다. 이러한 기법들을 바탕으로 55nm 공정에서 설계하여 calibration 없이도 93.3 dB의 높은 SNDR 및 156.25 kHz BW에서 180.4 dB의 Schreier FoM을 달성하면서 넓은 범위의 inter-stage gain error tolerance (-33%~+50%)를 확보하였다.

[그림 2] 논문 18.3에서 제안하는 cross-stage gain-mismatch error shaping 기법의 동작 원리

[그림 3] 논문 18.3에서 제안하는 Calibration-Free Pipelined SAR ADC 구조 및 timing diagram

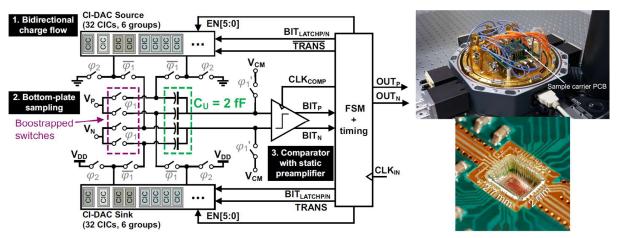

#18-8 벨기에 KU Leuven 대학에서 40.7 dB 의 SNDR 을 갖는 극저온 charge injection (CI) SAR ADC를 빌표하였다. 양자 얽힘 현상 구현을 위해 극저온 환경을 요하는 qubit의 readout 회로가 target application이며, 냉동고 cooling capacity를 고려하여 ADC 및 ADC driver 전력 소모를 최소 화할 수 있도록 medium-resolution SAR ADC의 input capacitance를 4 fF 수준으로 크게 줄일 수 있는 CI SAR 구조를 채택하였다. 기존 CI SAR 구조 [2]의 단점인 DAC common-mode voltage의 단조감소를 sinking 과 sourcing 모두 할 수 있는 complementary CI DAC를 적용하여 common-mode voltage가 일정하게 유지될 수 있도록 하였다. 또한 comparator kickback을 줄이기 위해 continuous-time preamplifier를 적용하였다. 이러한 기법들을 바탕으로 40nm 공정에서 제작하여 6.5K의 극저온에서도 40.7 dB의 SNDR을 달성하였고, 극저온에서 CI cell의 mismatch가 7-bit 해상 도를 달성하는 데에는 무리가 없음을 보여주었다.

[그림 4] 논문 18.8에서 제안하는 극저온 CI SAR ADC 구조 및 측정 환경

## **Session 24: High-Frequency ADCs**

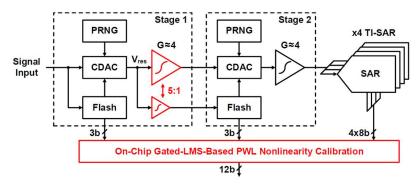

#24-1 중국 칭화대에서 single channel로 12b, 3 GS/s를 달성할 수 있는 pipelined ADC 구조를 제안하였다. Residue amplifier의 nonlinearity를 on-chip으로 구현된 hardware만으로 background calibration 하면서도 15.2 fJ/conv-step의 Walden FoM을 달성하였다. 전체 구조는 [그림 5]와 같이 3-stage이며, 두 개의 pipeline stage와 마지막 8b, 4-way TI SAR ADC를 backend로 구성되어 있다. 기존에 polynomial 기반으로 nonlinearity background calibration 하는 방식은 on-chip으로 구현하기에 복잡하므로, 입력전압 구간을 나누어 구간에 따라 piecewise-linear (PWL)하게 calibration 하는 방식을 제안하였다. 각 구간에 대해서 Residue 입력에 analog dither injection, Quantizer 출력에 digital dither subtraction 할 때 그 차이에 해당하는 gain error를 LMS 알고리즘으로 최소화하는 원리이며, [그림 6]과 같이 LSB에 해당하는 optimal gain (k1~k4) 중 k1은 LMS filter를 통해 항상 업데이트하고, k2~k4는 각 범위에서 MSB의 gain (b1~b3)보다 커질 때에만 LMS filter를 통해업데이트하는 adaptive threshold 방식이다. 이 때 MSB의 gain (b1~b3)은 k1~k4로 정해지고, stage 1과 2에 이러한 PWL nonlinearity calibration을 적용한다. 이러한 기법들을 바탕으로 28nm 공정에서 제작하여 single channel 기준 3 GS/s, 58.8 dB SNDR를 달성하였다. 최적의 PWL coefficient 및 SNDR은 대략 3ms 안에 수렴하며 +/-5%의 supply variation, -40~85°C의 온도 범위에서 SNDR 저하가 1.3 dB 이하로 유지할 수 있다.

[그림 5] 논문 24.1에서 제안하는 Pipelined ADC 전체 구조

[그림 6] 논문 24.1에서 제안하는 residue amplifier의 nonlinearity background calibration 방식

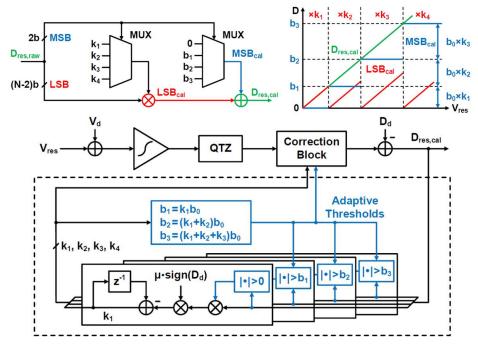

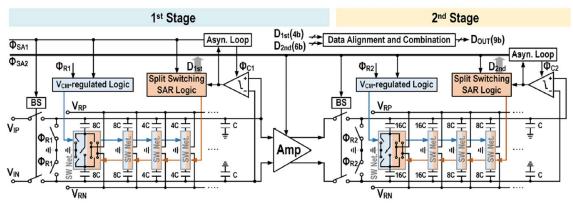

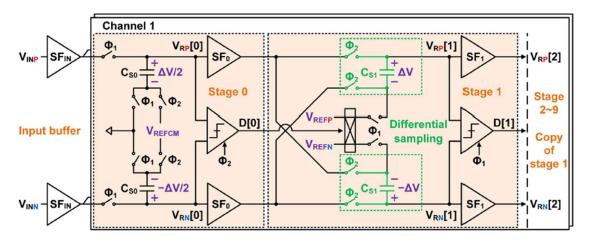

#24-5 중국 마카오 대학에서 72 GS/s, 9b, 64-way TI pipelined SAR ADC 를 제안하였다. ISSCC 2024 에서 발표된 논문들 [3], [4]과 비교하면 sampling rate 이 높지는 않지만 20GHz input 에서 41.0dB SNDR, 55.3dB SFDR 을 달성하여 선형성을 보다 향상시킨 구조이다. 전체 구조는 [그림 7]과 같이 T-coil 및 두 개의 입력 버퍼로 각각 even/odd 8 채널을 drive 하고, 각 채널에서 sample 된 신호가 sub-buffer 를 거쳐 1.125 GS/s 로 동작하는 4 개의 pipelined SAR ADC 로전달되는 구조이다. 입력 버퍼의 경우 conventional source follower (SF)의 단점인 1 보다 작은 gain, slewing 및 선형성 한계를 common-source (CS) 를 추가하여 보상하였다. Bandwidth mismatch의 주된 원인인 switch mismatch로 인한 SFDR 저하를 줄이기 위해 bootstrapped switch (BS)를 사용하되, critical node의 load cap을 줄일수 있는 split-path BS 구조를 제안하여 track time을 줄였다. Unit pipelined SAR ADC 구조는 [그림 8]과 같고, 첫 번째와 두 번째 stage에서 각각 4bit, 6bit를 resolve 하고 1-bit redundancy를 가지는 구조이다. Residue amplifier의 경우 저항의 비율로 gain 이 정해지는 ratiometric 구조를 사용하였다. 이러한 기법들을 바탕으로 16nm

FinFET 공정에서 제작되어 72 GS/s, 20GHz input 기준 41.9 dB SNDR, 55.3 dB SFDR, 53.7 fJ/c.-s Walden FoM, 151.5 dB Schreier FoM 을 달성하였다.

[그림 7] 논문 24.5에서 제안하는 전체 TI pipelined SAR ADC 구조

[그림 8] 논문 24.5에서 제안하는 Unit pipelined SAR ADC 구조

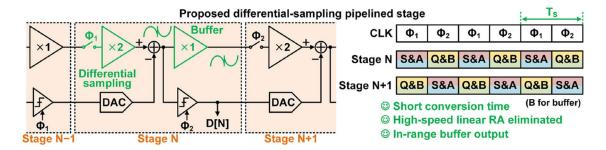

#24-7 중국 칭화대에서 8b, 10 GS/s 2X-TI pipelined ADC 구조를 제안하였다. 기존 conventional pipelined ADC의 경우 하나의 stage 내 동작이 sampling, quantization, amplification 3단계로 구성되고 고속의 linear residue amplifier (RA)가 필요하다는 단점이 있다. 제안하는 Pipeline ADC의 구조는 [그림 9]과 같이 sampling & amplification, quantization & residue buffering 2단계로 동작하여 conversion time을 줄일 수 있고, [그림 10]과 같이 RA 대신 differential sampling으로 2X passive amplification을 구현하여 power efficiency를 높였다. Buffer는 source follower (SF)로 구현하였는데 input transistor의 overdrive voltage를 크게 설계하여 별도의 switch 없이도 power gating할 수 있는 방식으로 differential sampling을 하고 있는 stage들의 SF 전력 소모를 저감하였다. 이러한 기법들을 바탕으로 28nm 공정에서 구현하여 41.7 dB의 SNDR, 2 channel로 10 GS/s, 22.0 fJ/conv-step의 Walden FoM를 달성하였다.

[그림 9] 논문 24.7에서 제안하는 pipelined ADC 구조 및 동작 원리

[그림 10] 논문 24.7 에서 제안하는 pipelined ADC 회로 구현

### 참고문헌

- [1] Y. -S. Shu, L. -T. Kuo, and T. -Y. Lo, "An Oversampling SAR ADC With DAC Mismatch Error Shaping Achieving 105 dB SFDR and 101 dB SNDR Over 1 kHz BW in 55 nm CMOS," IEEE Journal of Solid-State Circuits, vol. 51, no. 12, pp. 2928-2940, Dec. 2016.

- [2] K. D. Choo, J. Bell, and M. P. Flynn, "Area-efficient 1GS/s 6b SAR ADC with charge-injection-cell-based DAC," ISSCC, pp. 460-461, Feb. 2016.

- [3] G. Li et al., "A 600Gb/s DP-QAM64 Coherent Optical Transceiver Frontend with 4x105GS/s 8b ADC/DAC in 16nm CMOS," ISSCC, pp. 338-340, Feb. 2024.

- [4] R. L. Nguyen et al., "A 200GS/s 8b 20fJ/c-s Receiver with >60GHz AFE Bandwidth for 800Gb/s Optical Coherent Communications in 5nm FinFET," pp. 344 346, Feb. 2024.

# 저자정보

# 황영하 교수

● 소 속 : 숭실대학교 전자정보공학부

● 연구분야 : 데이터변환기 및 집적시스템 설계

● 이 메 일 : youngha@ssu.ac.kr ● 홈페이지 : https://aidl.ssu.ac.kr

## 2025 International Solid-State Circuits Conference

## (ISSCC) Review

중앙대학교 창의ICT공과대학 전자전기공학부 한동현 교수

#### **Topic: Al-Accelerators and Compute-In-Memory**

### **Session 14: Compute-In-Memory**

이번 ISSCC 2025의 Session 14는 인메모리 컴퓨팅 (In-memory Computing)을 주제로 총 7편의 논문이 발표되었다. 올 해 ISSCS에서 발표된 CIM은 총 3가지의 주요 트랜드를 보였다. 첫째, 작년에는 SRAM, DRAM, RRAM, FLASH 등 다양한 메모리를 활용한 CIM이 발표되었다면, 올 해는 한 편의 STT-MRAM 기반 CIM (논문 14.1) 한 편의 Gain Cell 기반 CIM (논문 14.2) 를 제외하면 모두 SRAM 기반 CIM을 발표하였다. 둘째, CIM에서 부동소수점을 어떻게 효율적으로 혹은 정확하게 지원할지에 집중하였다. (논문 14.2, 14.3, 14.4, 14.5) 셋째, 아날로그 (논문 14.1) 혹은 혼성 신호 기반 CIM (논문 14.6) 보다는 디지털 기반 CIM 관련 논문이 대다수였다.

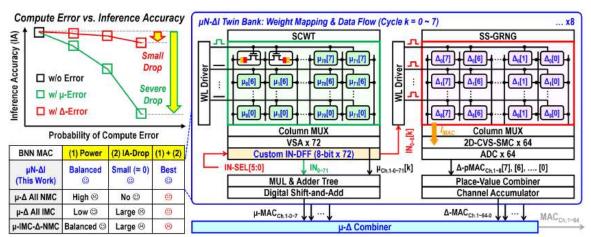

#14-1은 국립칭화대학교와 TSMC에서 공동 연구로 발표한 22nm STT-MRAM 기반 CIM 으로 다른 논문과 달리 특별히 Bayesian Neural Network (BNN) 가속을 목표로 설계된 것이 큰 특징이다. 특히 이미 값이 정해져 있는 기존 인공지능 연산과 달리 난수를 계속 생성해주어야 하는 BNN 연산 가속을 위해 MRAM에 Self-Compare Write-Termination 회로를 추가하였으며, 정확한 연산과 부정확한 연산이 필요한 부분을 구분해 따로 다른 최적화된 CIM 을 설계함으로써 에너지 효율을 극대화하였다. CIFAR-100 이라는 비교적 쉬운 데이터셋에서 ResNet-20 이라는 작은 인공지능 모델을 사용하였음에도, 1.19%의 상대적으로 높은 정확도 손실이 측정되는 점이 아쉽지만, 해당 측정 결과에서 기존 STT-MRAM 기반 CIM 대비 2.3배 높은 에너지 효율을 달성하였다.

[그림 1] "14.1. A 22nm 104.5TOPS/W μ-NMC-Δ-IMC Heterogeneous STT-MRAM CIM Macro for Noise-Tolerant Bayesian Neural Networks" 전체 아키텍처 구조

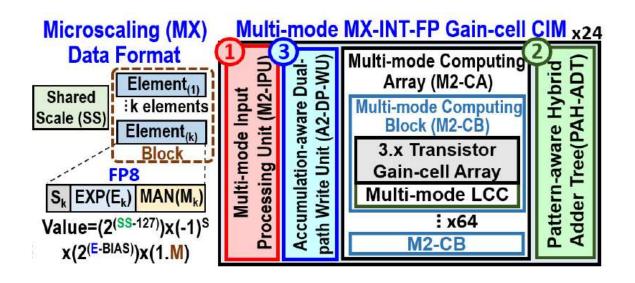

#14-2는 국립칭화대학교와 TSMC에서 공동 연구로 발표한 16nm Gain-cell 기반 CIM 으로 부동소수점 지원을 위해 흔히 사용하는 Shared exponent 혹은 Shared scale을 CIM 외부에 의존하지 않고, CIM 내부에서 모두 수행 가능하게 만듦으로써, 불필요한 데이터 전송을 최소화시킨 논문이다. 더불어, CIM에서 가장 많은 면적과 전력소모를 보이는 Adder tree의 오버헤드를 최소화 하기 위해 자주 나타나는 데이터 패턴만을 위해 최적화된 적은 트랜지스터를 사용한 Adder tree를 함께 활용하는 방식을 제안하였다. 해당 프로세서는 기존 프로세서 대비 1.8~2.5배 높은 FoM을 달성하여, Shared scale을 사용하는 MXINT8 포맷 데이터 연산시 133.5 TFLOPS/W를, INT8 지원시 205.4 TOPS/W 에너지 효율을 달성하는데 성공하였다.

[그림 1] "14.1. A 22nm 104.5TOPS/W μ-NMC-Δ-IMC Heterogeneous STT-MRAM CIM Macro for Noise-Tolerant Bayesian Neural Networks" 전체 아키텍처 구조

#14-5는 Institute of Microelectronics Chinese Academy of Sciences에서 발표현 28nm SRAM 기반 CIM으로 다른 CIM과 달라 Edge에서의 추론과 학습 모두를 지원한다고 주장한다. 이전에도 학습을 지원한다고 주장했던 CIM 논문이 있었지만, 추론과 오류 전사가 독립된 CIM에서 수행되었던 단점을 지적하면서, 이를 통합하고, 부동소수점 연산 지원과 전치 행렬 연산을 동시에 수행하는 CIM 을 설계하였다. 하지만 학습의 주요과정인 가중치 업데이트가 생략되었다는 점, 제작한 프로세서를 측정하기 위해 사용한 CIFAR-10과 CIFAR-100이 비교적 쉬운 데이터셋이라는점, 사용한 AI 모델역시 너무 단순하다는점이 아쉽다. 오류를 감수하더라도 근사 연산을 수행하거나, 학습 등을 위해 정확한 연산을 함께 수행할 수 있는 MAC이 집적되어 있어, 근사 연산수행시 192.3 TFLOPS/W 의 에너지 효율을 달성하였다.

#### Session 23: Al-Accelerators

이번 ISSCC 2025의 Session 23은 인공지능 가속기를 주제로 총 10편의 논문이 발표되었다. 올 해 ISSCS에서 발표된 인공지능 가속기 (Session 2의 일부 논문 제외)는 총 2가지의 주요 트랜드를 보였다. 첫째, 확산 모델 (Diffusion Model)을 포함한 생성형 인공지능 (Generative AI, GenAI) 가속의 중요성이 많이 강조되었다. (논문 23.3, 23.5, 23.6, 23.10) 둘째, Large Language Model (LLM) 혹은 트랜스포머 (Transformer) 가속이 여전히 강조되고 있다. (논문 23.1, 23.2, 23.8, 23.9) 주요했던 아이디어 트랜드로 보았을 때는, 첫째, 하드웨어 리소스를 최대한 잘 활용하기 위한 컴파일러, 스케줄러의 중요성이 강조되었다. (논문 23.2, 23.5) 둘째, 채널 별, 타임스텝 별 유사도를 이용해 손실없이 고효율 연산을 수행하는 고정소수점 기반 혼합 정밀도 연산 (논문 23.3, 23.7, 23.10), 혹은 고정소수점-부동소수점 혼합 연산 (논문 23.6, 23.8)을 채택하였다. 셋째, 에너지 효율을 더 높이기 위해 이형 코어 (Heterogeneous Core) 구조의 중요성이 강조되었다. (논문 23.1, 23.6, 23.10) 넷째, 프로세서 자체의 에너지 효율도 중요하지만, 외부 메모리 접근량 (External Memory Access, EMA)감소의 중요성이 강조되었다. (논문 23.1, 23.2, 23.3, 23.5, 23.6, 23.8, 23.9)

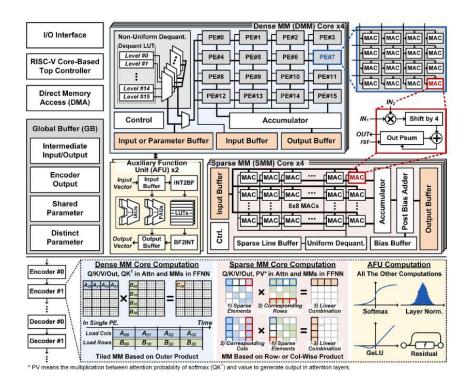

#23-1은 Columbia University에서 발표한 16nm Fin-FET 기반 트랜스포머 가속기로, Factorizing Training이라는 새로운 학습 기법을 적용해 레이어마다 공유하는 가중치를 학습하고, 이를 통해 트랜스포머 추론 가속시 외부메모리 접근량을 크게 줄이는데 성공하였다. 특히 Factorizing Training으로 인해 모든 레이어에서 공유되는 가중치는 데이터 희소성이 높지 않지만, 레이어마다 독립적으로 갖는 가중치는 데이터 희소성이 높은 특성을 활용하기 위해 이형 코어 구조를 채택한다. 이때 2개의 서로 다른 이형 코어가 메모리에 다르게 접근하여 생기는 문제를 해결하기 위해, load / store 동작을 수평 / 수직 방향에서 동시에 수행할 수 있는 Two-Direction Accessible Register File을 함께 설계하였다. Factorizing Training기반 최적화를 통해, 본 논문은 32~66배 적은 외부 메모리 접근량을 달성하는데 성공하였다.

#23-2는 홍콩과학기술대학에서 발표한 28nm 기반 트랜스포머 가속기로, 트랜스포머 연산 중 발생하는 Queue, Key, Value로 인한 외부메모리 접근량을 최소화하기 위해 Attention 연산을 Softmax를 제대로 활용하는 Vanilla Attention과 선형 근사하는 Linear Attention 으로 나누어 처리하는 방식을 채택했다. 해당 방식은 정확도 손실과 Trade-off 관계임을 밝히고 있으며, 레이어마다최적의 Vanilla Attention/ Linear Attention 비율을 찾아주어야 최적의 효율이 나올 수 있다. 뿐만아니라, Linear Layer 은 뒤에 이어지는 Convolution layer와 합쳐질 수 있으므로, 연산량을 최소화하고 코어 활용도를 극대화 하기 위해, 런타임 Layer Fusion 스케줄러를 같이 결합한 것이 특징이다. 본 논문 역시 25.9배 적은 외부 메모리 접근량을 보이면서 이를 통해, 4.6배에서 7.1배 높은추론 속도와 4.4~7.1배 적은 시스템 에너지 소모를 달성하였다.

[그림 1] "23.1. T-REX: A 68-to-567µs/Token 0.41-to-3.95µJ/Token Transformer Accelerator with Reduced External Memory Access and Enhanced Hardware Utilization in 16nm FinFET" 전체 아키 텍처 구조

[그림 1] "23.2. A 28nm 0.22µJ/Token Memory-Compute-Intensity-Aware CNN-Transformer Accelerator with Hybrid-Attention-Based Layer-Fusion and Cascaded Pruning for Semantic-Segmentation" 전체 아키텍처 구조

#23-8은 칭화대에서 발표한 28nm 기반 트랜스포머 가속기로 23.1과 23.2처럼 학습 자체를 새롭게 하여 추론시 성능을 높이는 방식이 아닌 주어진 트랜스포머 구조 가속에 집중한 논문이다. 마찬가지로 트랜스포머 가속시 발생하는 많은 외부 메모리 접근량을 해결하기 위해, KV 캐시를 효율적으로 압축할 수 있는 방식과 고정소수점-부동소수점을 함께 활용하는 방식을 채택하였다. 특히 누적기에서 필요로 하는 비트수를 획기적으로 줄이기 위해 비슷한 Exponent 별로 모아서 연산하는 Processing Element를 고안하였다.

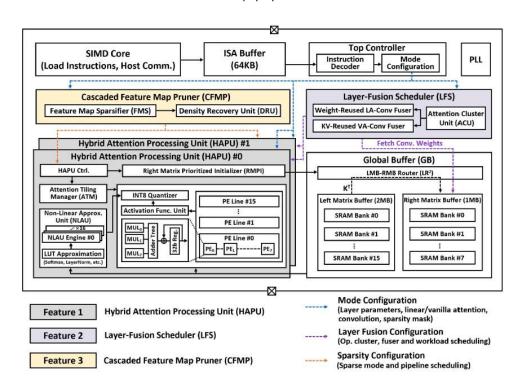

#23-9는 KAIST에서 발표한 28nm 기반 LLM 가속기로, 많은 외부 메모리 접근 문제와 연산 효율 극대화를 위해 Binary / Tenary로 양자화된 LLM 을 가속한다. 낮은 비트수로 양자화 되면서 가중 치에서 보이는 비슷한 패턴을 최대한 재사용하여 처리량을 늘리고, 가중치의 순서까지 조절해, 발생할 수 있는 Bit Toggling을 최소화한다. 이렇게 Binary / Ternary 가중치로 양자화된 LLM 전용 가속기는 이전 LLM 가속기 대비 4.6배 높은 에너지 효율 달성에 성공하였다.

[그림 1] "23.9. Slim-Llama: A 4.69mW Large-Language-Model Processor with Binary/Ternary Weights for Billion-Parameter Llama Model" 전체 아키텍처 구조

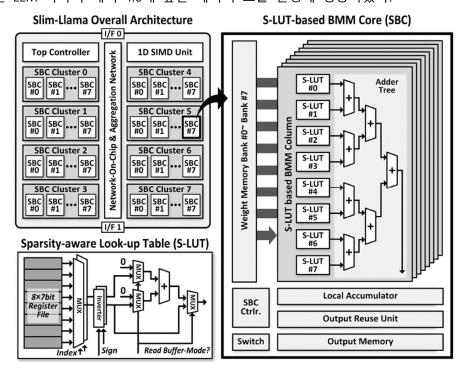

#23-3은 KAIST에서 발표한 28nm 기반 확산 모델 가속기로, 기존 여러 반복을 거쳐서 최종 출력을 만들어 내는 확산 모델의 단점을 해결하기 위해 나온 Few-shot 확산 모델 가속을 목표로 한다. 타임 스텝별로 유사도를 파악하고 이를 활용하던 기존 프로세서의 연산 특성을 사용할 수 없으므로, 중요도가 높은 채널들끼리 혹은 중요도가 낮은 채널들 끼리 묶고 유사한 채널들 사이에서 고정소수점으로 표현할 때 필요한 비트수를 최적화하는 방식을 채택하고, 채널별로 연산을 묶어 연산기를 최적화 하는 방식을 제안하였다. Few-shot 확산 모델과 이에 최적화된 양자화 기법을 토대로 기존 확산 모델 가속기 대비 3.3~6.8배 낮은 에너지 소모를 달성에 성공하였다.

[그림 1] "23.3. EdgeDiff: 418.4mJ/Inference Multi-Modal Few-Step Diffusion Model Accelerator with Mixed-Precision and Reordered Group Quantization" 전체 아키텍처 구조

- #23-5는 MediaTek에서 발표한 3nm 기반 생성형 인공지능을 위한 엣지 디바이스용 프로세서로, 256KB의 아주 적은 온칩 메모리로 Convolution, 행렬곱 연산을 수행하기 위해 Layer Fusion을 최대한 활용할 수 있는 스케줄링을 제안하며, 특히 라인별 데이터가 준비되는 대로, 다음 레이어 연산을 바로 수행하는 것이 특징이다. 이런 연산을 구현하기 위해 라인 데이터를 저장하는 캐시를 별도로 둔 것이 아키텍처 수준에서 가장 큰 차별점이며, Branch가 있을 경우지연 시간 최소화를 위해, 컴파일러 수준 최적화를 동시에 진행하였다. 본 프로세서가 3nm 기반으로 만들어졌다는 점, 0.168 mm²의 작은 면적에 다양한 생성형 인공지능 연산 수행을 위한 스케줄링, 아키텍처, 컴파일러 최적화 기법이 들어간 점이 다른 논문들과의 차별점이라볼 수 있다.

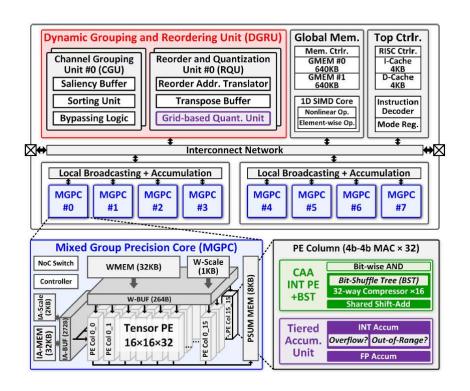

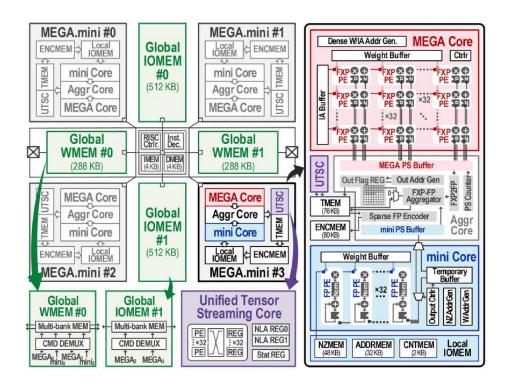

- #23-6은 MIT에서 발표한 28nm 기반 생성형 인공지능 가속기로 CNN, 트랜스포머, 확산 모델 등, 모델과 어플리케이션에 제한없이 정확도 손실을 최소화하면서 효율적으로 가속할 수 있는 방법을 제안한다. 특히 Inlier 입력은 고정소수점으로, Outlier 입력은 부동소수점으로 표현하는 방식을 채택하고, 데이터 재사용을 극대화한 고정소수점 전용 가속기와 데이터 희소성을 활용하는 부동소수점 기반 가속기를 모두 활용하는 아키텍처가 특징이다. 본 논문은 CPU의 빅/리틀 코어아키텍처처럼 NPU도 새로운 빅/리틀 코어 아키텍처 (메가/미니)가 필요함을 강조하였다. 뿐만아니라, 최신 AI 모델에서 많이 사용되는 정규화 및 비선형 함수 가속 방법 역시 함께 제안한다. 판별형, 생성형 AI 상관없이 84% 이상의 높은 에너지 효율을 달성하였으며, 기존 확산 모델전용 가속기와 비교하여도, 2.1배 높은 추론 속도와 3.4배 높은 에너지 효율을 달성하였다.

[그림 1] "23.6. MEGA.mini: A Universal Generative AI Processor with a New Big/Little Core Architecture for NPU" 전체 아키텍처 구조

### 저자정보

### 한동현 교수

● 소 속 : 중앙대학교 창의ICT공과대학 전자전기공학부

● 연구분야: Digital Architecture & SoC Design

• 이 메 일 : hdh4797@cau.ac.kr

• 홈페이지 : https://hdh4797.wixsite.com/dhan

## 2025 International Solid-State Circuits Conference

# (ISSCC) Review

아주대학교 지능형반도체공학과 이종민 교수

**Topic: Security**

#### **Session 17: Hardware Security**

이번 ISSCC 2025의 Session 17은 Hardware Security라는 주제로, 동형 암호 가속에 대한 논문 2편, Physically Unclonable Function (PUF) 논문 2편, 그리고 Side-channel attack 방지 회로에 대한 논문 2편이 발표되었다. 특히, 작년에 이어 동형 암호 가속에 대한 논문이 발표되고 있는 점과, PUF의 새로운 안정화 방법에 대한 논문이 발표되고 있음을 주목할 만 하다.

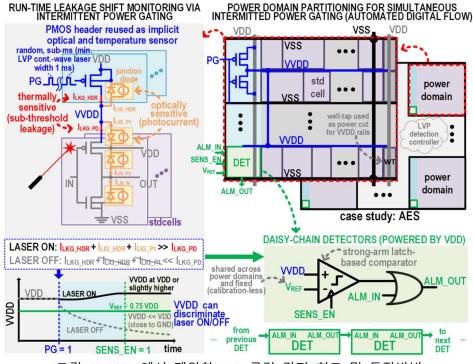

#17-1 은 National University of Singapore에서 제안한 논문으로, LVP (Laser Voltage Probing) 공격을 탐지하는 회로를 제안하였다. 기존의 탐지 회로들은 PVT (Process, Voltage, Temperature)에 취약하거나, 면적 overhead가 큰 한계가 있었다. 그러나, 제안하는 연구에서는 추가적인 센서 없이 PMOS sleep transistor를 활용하여 LVP 공격을 감지하였다. 일정 영역별로 PMOS header, DET 구조를 배치하고, laser attack이 감지되는 경우 DET의 strong-arm latch에서 ALM 신호가 활성화 되도록 설계하였다. 넓은 영역의 LAP 공격을 감지하기 위해 ALM 신호를 DET끼리 연결하여 최종 ALM 신호를 생성하도록 하였다. 이를 통해 4.35%의 area overhead 만으로도 LAP 공격을 감지하는 구조를 설계하였다.

[그림 1] #17-1에서 제안한 LVP 공격 감지 회로 및 동작방법

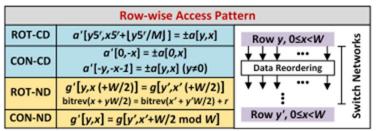

#17-3 은 National Taiwan University에서 발표한 논문으로, multi-key CKKS 알고리즘 가속을 위한 프로세서를 제안하였다. 특히, NTT (Number Theoretic Transform)이 가장 많은 작업이므로, NTT를 기준으로 최적화하여 연산 속도를 향상시켰다. 또한, 불규칙한 데이터 접근 패턴을 가지는 ROT, CON 연산들에 대해 기존보다 빠르게 수행할 수 있도록 효율적인 dataflow를 설계하였다.

[그림 2] #17-3에서 제안한 ROT, CON 연산

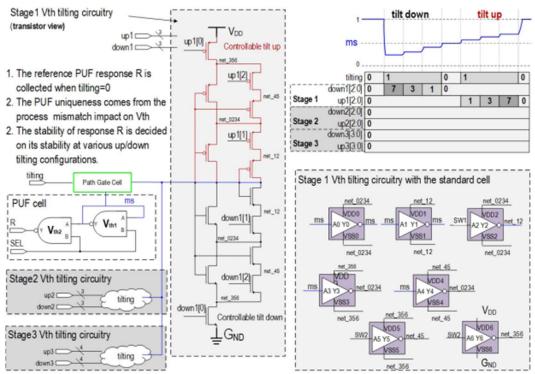

#17-4 은 삼성전자 Foundry 사업부에서 발표한 논문으로, 2016년 및 2020년도 ISSCC에 발표한 PUF의 구조에 tilting 기법을 적용하였다. PUF의 cell 구조는 2016년도에 개발된 NAND gate를 직렬로 연결한 구조를 활용하고 있으며, 본 논문에서 주목할 점은 controllable tilting 구조를 제안하였다는 점이다. 특히, controllable tilting 회로는 standard inverter cell로 간단하게 구현할 수 있어, non-recurrent engineering cost를 낮출 수 있는 부분 중 하나이다. Tilting 회로는 NAND gate들 간의 mismatch가 작아 unstable한 response를 생성하는 cell들을 screening 하여 제거할 수 있다. 제안하는 구조는 8nm FinFET, 3nm GAA 공정에서 제작되었으며, 다양한 corner, temperature, supply voltage에 따라 reproducibility를 검증하였다. 또한, NIST SP 800-90b test를 통해 non-IID entropy estimation score도 검증하였다.

[그림 3] #17-4에서 제안한 controllable tilting 회로 및 제어 방법

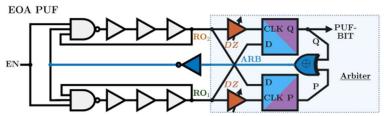

#17-5 은 독일 University of Ulm에서 발표한 논문으로, [그림 4]와 같은 Arbiter PUF 구조를 활용하여 random response를 생성하였다. 본 논문의 장점으로는 자동화된 에러 감지 기능으로, response의 unstable한 state와 noisy한 state를 구분하여 분석하였다. [그림 5]의 좌측과 같이 안정적이고 noise robust한 cell들 만을 원하지만, 가운데 그림과 같이 noise에 취약하거나, 우측 그림과 같이 외부 환경 변화에 따라 response가 뒤집히는 현상이 발생한다. 이렇게 불안정한 response를 스스로 감지하기 위해, ARB신호를 생성하였고, ARB 신호가 0인 경우 readout을 반복하여 자동화된 에러 감지를 가능케 하였다.

[그림 4] #17-5에서 제안한 EOA PUF 구조

[그림 5] #17-5의 온도 및 supply voltage의 변화에 따른 RO의 frequency

#17-6 은 NVIDIA에서 발표한 논문으로, clock glitch 공격을 탐지하면서 안정적인 reference clock을 제공하는 RC oscillator를 제안하였다. [그림 6]의 제안하는 구조는 90°씩 shift된 4-phase의 clock을 sampling하여, glitch를 감지하였다. 또한 clock-glitch filter를 통해 1/4F<sub>VCO</sub> 보다 짧은 pulse를 filtering 하였다.

#### 참고문헌

**#17-1** H. Zhang, et al., "Sensor-Less Laser Voltage-Probing Attack Detection via Run-Time-Leakage-Shift Monitoring with 4.35% Area Overhead," *IEEE International Solid-State Circuits Conference (ISSCC)*, Feb. 2025.

**#17-3** L-H. Lin, et al., "A 30.4GOPS/mW MK-CKKS Processor for Secure Multi-Party Computation," *IEEE International Solid-State Circuits Conference (ISSCC)*, Feb. 2025.

**#17-4** B. Karpinskyy, et al., "An Efficient V<sub>th</sub>-Tilting PUF Design in 3nm GAA and 8nm FinFET Technologies," *IEEE International Solid-State Circuits Conference (ISSCC)*, Feb. 2025.

**#17-5** B. Driemeyer, et al., "An Eye-Opening Arbiter PUF for Fingerprint Generation Using Auto-Error Detection for PVT-Robust Masking and Bit Stabilization Achieving a BER of 2e-8 in 28nm CMOS," *IEEE International Solid-State Circuits Conference (ISSCC)*, Feb. 2025.

**#17-6** N. Metha, et al., "A 100MHz Self-Calibrating RC Oscillator Capable of Clock-Glitch Detection for Hardware Security in a 3nm FinFET Process," *IEEE International Solid-State Circuits Conference (ISSCC)*, Feb. 2025.

### 저자정보

### 이종민 교수

● 소 속 : 아주대학교 지능형반도체공학과

• 연구분야 : Hardware Security Circuits, Post-Quantum Cryptography Accelerators, Low-power Digital Circuits

• 이 메 일 : jongmin@ajou.ac.kr

• 홈페이지 : https://sites.google.com/ajou.ac.kr/aisic

## 2025 International Solid-State Circuits Conference

# (ISSCC) Review

연세대학교 시스템반도체공학과 최경식 교수

Topic: RF

### Session 10: Transceiver Chipsets for Communication and Radar

이번 ISSCC 2025의 Session 10은 **Transceiver Chipsets for Communication and Radar**라는 주제로 총 5편의 논문이 발표되었다. 이 세션에서는 무선 통신 및 레이더 센싱을 응용으로 하는 다양한 송수신기 시스템 칩셋을 조명하였다. 또한 RF Front-end 혹은 power amplifier와 phase shifter 같은 개별 블록은 Session 5, Session 11, 그리고 Session 33에서 찾아볼 수 있다.

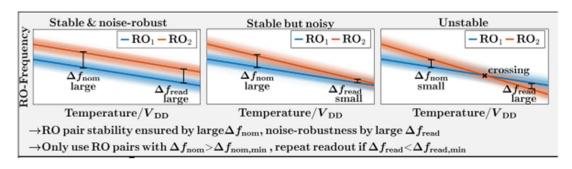

#10-1 본 논문은 East China Normal University에서 연구한 77GHz 하이브리드 TDMA-MIMO 위상 배열 FMCW 레이더에 관한 연구이다. 기존 MIMO 및 RF 위상 배열 레이더는 긴 탐지 거리와 높은 거리 해상도를 동시에 달성하기 어려웠으며, 단일 채널 송수신 구조로는 LRR (Long-Range Radar), MRR (Medium-Range Radar), SRR (Short-Range Radar) 모드를 모두 지원하는 것이 제한적이었다. 이를 해결하기 위해 본 논문에서는 8TX 및 2×4RX 구조를 갖춘 77GHz TDMA-MIMO FMCW 레이더를 제안하여 다양한 탐지 모드에서 최적의 성능을 제공하도록 설계하였다. 특히 Zig-Zag 다중 서브밴드 주파수 스위핑 기법을 활용하여 위상 잡음을 줄이면서 연속적인 주파수 변화를 가능하게 하였으며, 이를 통해 8GHz의 넓은 Chirping 대역폭을 확보하였다. 측정 결과, 제안된 레이더 송수신기는 32dBm EIRP 출력과 16.8dB의 잡음 지수를 달성하였으며, 186m의 탐지범위와 3cm의 거리 해상도를 보이며 기존 대비 향상된 성능을 보여주었다.

[그림 1] Session 10.1 논문에서 제안하는 하이브리드 TDMA-MIMO Phased-Array 레이더의 시스템 블록 다이어그램.

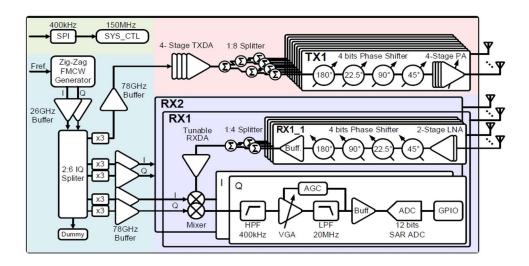

#10-2 본 논문은 Tianjin University에서 연구한 132-148GHz FMCW 레이더 송수신기에 대한 연구이다. D-밴드(110-170GHz)의 넓은 가용 대역폭을 활용한 고해상도 레이더 시스템이 주목받고 있으나, 기존 실리콘 공정(CMOS/SiGe) 기반 D-밴드 FMCW 레이더는 낮은 출력 전력과 안테나 이득으로 인해 충분한 EIRP를 제공하지 못했다. 본 논문에서는 4TX-4RX 배열을 갖춘 132-148GHz FMCW 레이더 송수신기를 제안하며, cavity-backed Antenna-in-Package (AiP)를 구현하여 방사 효율을 높이고 LTCC 패키지를 활용하여 손실을 최소화하였다. 또한 서브 하모닉 믹싱을 사용하여전력 소비를 줄이고 효율적인 신호 처리를 가능하게 하였다. 측정 결과, 제안하는 레이더는 28.7dBm의 EIRP를 달성하였으며, 7.8dB의 최소 잡음 지수와 최대 24GHz의 Chirp 대역폭을 달성하여 기존 대비 향상된 거리 해상도를 확보하였다.

[그림 2] Session 10.2 논문에서 제안하는 140 GHz 4TX-4RX FMCW Radar 송수신기 어레이 시스템의 블록 다이어그램.

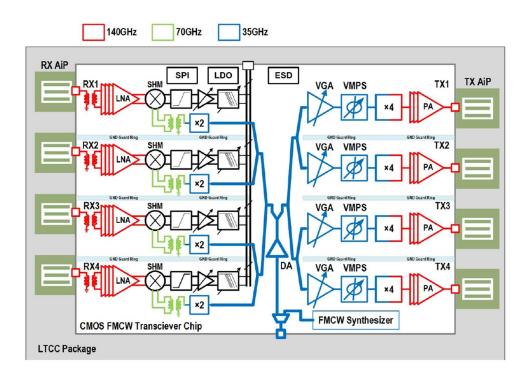

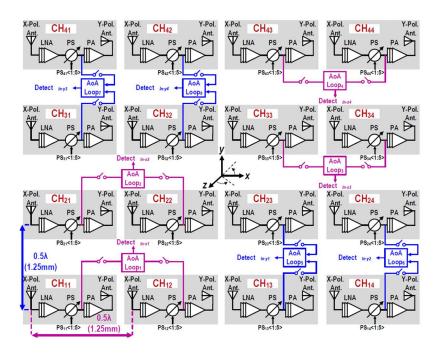

#10-3 본 논문은 ETH Zürich에서 연구한 120GHz 2D 확장형 능동 반사 릴레이에 대한 연구이다. 고주파(mmWave 및 sub-THz) 통신에서는 높은 주파수 대역의 특성상 자유 공간 손실(Free Space Path Loss)이 크며, 비가시선(Non-Line-Of-Sight) 환경에서는 신호 감쇠가 심하여 신호 전송이 어려운 문제가 있다. 이를 해결하기 위해 본 논문에서는 120GHz 대역에서 동작하는 2D 확장형 능동 반사 릴레이를 제안하였다. 온칩 송·수신 안테나를 직교 편광 방식으로 구성하여 송·수신 간간섭을 최소화하였다. 또한, 신속한 AoA(Angle of Arrival) 검출 기능을 내장하여 외부 디지털 백엔드 없이도 즉각적인 신호 방향 탐지가 가능하도록 설계하였다. 측정 결과, 본 릴레이는 1.3m 거리에서 6Gb/s의 데이터 전송 속도를 달성하였으며, 3.4~5% of EVM를 유지하며 안정적인 NLOS 링크를 제공하는 것을 확인하였다.

[그림 3] Session 10.3 논문에서 제안하는 120 GHz 2-D scalable 4×4 active reflective relay 시스템의 블록 다이어그램.

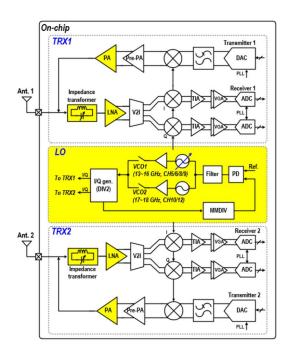

#10-4 본 논문은 삼성전자에서 연구한 2-TRX IR-UWB 송수신기 구현에 관한 연구이다. 기존 IR-UWB 송수신기는 한정된 채널 (ch5, ch9)만을 지원하며, 구현 측면에서는 TX/RX 안테나 공유를 위해 RF 스위치를 주로 사용되었다. 따라서 이 스위치의 높은 삽입 손실로 인해 수신 감도가 저하되는 문제가 있었다. 본 논문에서는 LC passive 네트워크를 활용하여 RF 스위치 없이 TR와 RX가하나의 포트를 공유하는 구조를 제안함으로써 삽입 손실을 최소화하고 수신 성능을 향상시켰다. 또한, 총 6개의 UWB 채널(6.5~9GHz)을 지원하며, 저전력 동작을 고려하여 두 개의 LC-VCO를 활용한 전력 최적화 기법을 적용하였다. 측정 결과, 본 연구에서 구현한 송수신기는 최대 14dBm의 송신 출력과 4.2dB 이하의 잡음 지수를 기록하였으며, IEEE 802.15.4/4z 표준을 준수하면서도 모바일 및 자동차 응용에 적합한 성능을 입증하였다.

[그림 4] Session 10.4 논문에서 제안하는 IR-UWB용 2-TRX Transceiver 시스템의 블록 다이어그램.

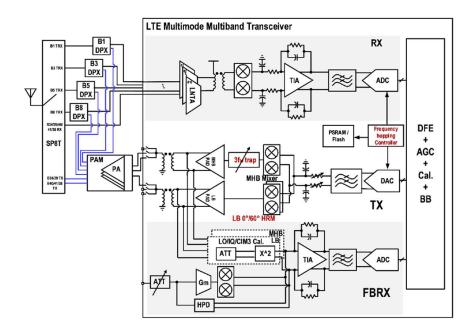

#10-5 본 논문은 XINYI Information Technology에서 연구한 LTE Cat1bis 지원 멀티모드 RF 송수신 기에 관한 연구이다. IoT 기기에서 LTE Cat1bis는 비용 효율적인 저속 데이터 전송 옵션으로 주목받고 있으나, 기존 송수신기 모듈은 패키징 및 보드 설계의 복잡성으로 인해 비용 절감이 어려웠다. 본 논문에서는 QFN 패키지를 적용하여 저비용 LTE Cat1bis RF 송수신기를 구현하였다. 먼저, RX 체인에서 단일 발룬 설계를 통한 10개의 저잡음 증폭기(LNTA) 공유 기법을 도입하여 전체 시스템 비용을 줄였다. 또한, 수신 감도 저하 문제를 해결하기 위해 ADC 주파수 호핑 기법을 활용하여 스퍼 노이즈를 차단하였다. 송신의 경우에는, 인덕터의 최적화 설계를 통해 3차 상호변조 왜곡(CIM3)을 억제하는 자동 보정 기능을 포함하여 선형성을 개선하였다. 측정 결과, 제안된 송수신기는 0.6~2.7GHz 대역의 동작 주파수 범위에서 우수한 수신 감도(~ -100dBm)을 달성하여 IoT 응용에 최적화된 성능을 제공하는 것을 확인하였다.

[그림 5] Session 10.5 논문에서 제안하는 LTE Cat1bis를 지원하는 multimode multiband RF transceiver 시스템의 블록 다이어그램.

### 저자정보

### 최경식 교수

● 소 속 : 연세대학교 시스템반도체공학과

● 연구분야: RF/mmWave/Sub-THz circuits and systems

• 이 메 일 : kyungsik@yonsei.ac.kr

• 홈페이지 : https://sites.google.com/view/year-yonsei/home